Inhaltsverzeichnis:

- Schritt 1: Blockschaltbild

- Schritt 2: Funktionsprinzip

- Schritt 3: Logikimplementierung

- Schritt 4: Deadlock auflösen

- Schritt 5: Gerätekonfiguration - Matrix0-Schaltung

- Schritt 6: Gerätekonfiguration - SPI-Taktlogik

- Schritt 7: Gerätekonfiguration - Eigenschaften der Matrix0-Komponenten

- Schritt 8: Gerätekonfiguration - Matrix1-Schaltung

- Schritt 9: Gerätekonfiguration - 3-Bit-Binärzähler

- Schritt 10: Gerätekonfiguration - 3-Bit-Vergleichslogik

- Schritt 11: Gerätekonfiguration - Digitale Vergleichslogik und temporäres Register

- Schritt 12: Gerätekonfiguration - Eigenschaften der Matrix1-Komponenten

- Schritt 13: Ergebnisse

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:16.

- Zuletzt bearbeitet 2025-06-01 06:08.

Steuersysteme und zugehörige Geräte arbeiten mit mehreren Stromquellen, wie zum Beispiel Vorspannungsleitungen oder Batterien, und müssen die höchste (oder die niedrigste) Leitung eines gegebenen Satzes verfolgen.

Zum Beispiel erfordert die Lastumschaltung in einem mit mehreren Batterien betriebenen System, dass das System entweder die minimale oder die maximale Spannung innerhalb des Batteriefelds überwacht (max oder min als Funktion des jeweiligen Schaltalgorithmus) und die Last dynamisch an die am besten geeignete Quelle in Echtzeit. Alternativ muss das System möglicherweise vorübergehend die Batterie mit der niedrigsten Spannung trennen, um ein ordnungsgemäßes Laden zu gewährleisten.

Ein weiteres Beispiel ist das moderne Solarstromsystem, bei dem jedes Solarpanel mit einem Tiltrotate-Mechanismus und einem Solar-Tracking-Schaltkreis ausgestattet ist (letzterer liefert die Sonnenstandsinformationen zur Ausrichtung des Panels). Mit den Max-Voltage-Infos kann jede Solarmodulposition auf der Grundlage der tatsächlich höchsten Ausgangsspannung des Stringpanels feinjustiert werden, wodurch eine überlegene Leistungsoptimierung erreicht wird.

Es gibt mehrere verschiedene Marken kommerzieller ICs (hauptsächlich Mikrocontroller), die im Prinzip einen maximalen Spannungsfolger implementieren können. Sie erfordern jedoch eine Programmierung und sind weniger kosteneffektiv als eine Mixed-Signal-Lösung. Die Ergänzung eines Dialog GreenPAKTM-Designs kann sich positiv auf die Erschwinglichkeit, Größe und Modularität des Designs auswirken. Dieses Design nutzt den Vorteil, sowohl analoge als auch digitale Schaltungen in einem einzigen Chip zu integrieren.

In diesem Instructable sind das analoge Front-End und die digitale Logik implementiert, die zum Implementieren eines maximalen (oder möglicherweise minimalen) Spannungsfinders unter acht verschiedenen Quellen erforderlich sind.

Zur Implementierung der 8-kanaligen analogen Max/Min-Spannungsüberwachung wird ein SLG46620G verwendet.

Im Folgenden haben wir die erforderlichen Schritte beschrieben, um zu verstehen, wie die Lösung programmiert wurde, um den analogen 8-Kanal-Max/Min-Spannungsmonitor zu erstellen. Wenn Sie jedoch nur das Ergebnis der Programmierung erhalten möchten, laden Sie die GreenPAK-Software herunter, um die bereits fertige GreenPAK-Designdatei anzuzeigen. Schließen Sie das GreenPAK Development Kit an Ihren Computer an und klicken Sie auf das Programm, um den analogen 8-Kanal-Max/Min-Spannungsmonitor zu erstellen.

Schritt 1: Blockschaltbild

Die Abbildung 1 zeigt das globale Diagramm des implementierten Systems.

Ein String von bis zu 8 variablen Spannungsquellen wird gemultiplext und mit einem ADC-Modul von GreenPAK verbunden, das mit einem kundenspezifischen internen Design verbunden ist, das in der Lage ist, die Quelle mit der höchsten Spannung im Vergleich zu den anderen auszuwählen. Die interne Logik gibt diese Informationen zur Anzeige oder Weiterverarbeitung aus.

Das Design basiert auf dem GreenPAK Produkt SLG46620G, da es alle notwendigen analogen und digitalen Bausteine für die Anwendung einbettet. Bei dieser Implementierung wird das Array mit einem ADG508-Analogmultiplexer abgetastet, der direkt vom GreenPAK-IC angesteuert wird.

Die Ausgangsinformationen sind eine digitale 3-Bit-Zahl, die der Nummer der Spannungsquelle bei maximaler Spannung entspricht. Eine direkte Möglichkeit, diese Informationen zu erhalten, besteht darin, die Nummer über eine 7-Segment-Anzeige anzuzeigen. Dies kann leicht erreicht werden, indem der digitale Ausgang des SLG46620G an einen 7-Segment-Anzeigetreiber wie die in der Referenz beschriebene GreenPAK-Lösung oder an einen üblichen 74LS47-IC angeschlossen wird.

Die vorgestellte Schaltung sucht nach maximaler Spannung. Um das Design in einen Minimalspannungssucher umzuwandeln, muss eine einfache Vorkonditionierungsschaltung zwischen dem analogen Multiplexer und dem GreenPAK-Analogeingang hinzugefügt werden, wobei der Multiplexerausgang von einer 1 V-Referenzspannung subtrahiert wird.

Schritt 2: Funktionsprinzip

Das Design zielt darauf ab, die Quelle mit maximaler Spannung auszuwählen, daher wird ein Scan auf dem gesamten Array durchgeführt, während der letzte maximale Wert gespeichert und mit dem nächsten Wert im Eingang (der zur nächsten Spannungsquelle im Scan gehört) verglichen wird.

Im Folgenden bezeichnen wir eine komplette Multiplexing-Sequenz entlang aller Eingänge als „Scan“oder „Loop“.

Der Vergleich zweier Werte erfolgt nicht über ACMP-Komponenten (allerdings im SLG46620G vorhanden), sondern über das DCMP-Modul, nachdem die Werte jeweils digitalisiert wurden. Dies ist eine fortgeschrittene und verfeinerte Technik, die erstmals in der Referenz behandelt wird.

Abbildung 2 zeigt, wie das SLG46620G für dieses Design aufgebaut ist.

Das analoge Eingangssignal wird über die PGA-Komponente mit einem eingestellten Gain von 1 zum ADC-Eingang geleitet. Es sind auch verschiedene Gain-Einstellungen möglich, um die beste Anpassung an die Front-End-Konditionierungselektronik zu finden, die die Eingangsspannungen auf 0-1 V. abbildet Reichweite des GreenPAK ADC-Moduls.

Der ADC arbeitet im Single-Ended-Modus und wandelt das analoge Signal in einen 8-Bit-Digitalcode um, der dann an das DCMP-Modul übertragen wird. Der digitale Code wird auch in den SPI-Block eingespeist, der als ADC/FSM-Puffer konfiguriert ist, wo ein digitaler Code gespeichert werden kann und sich nicht ändert, bis der nächste Impuls am SPI-CLK-Eingang ankommt. Beachten Sie, dass ein dedizierter Logikblock den SPI CLK-Eingang steuert. Wir werden diesen Teil später untersuchen, da dies die „Kern“-Logik ist, die für den ordnungsgemäßen Betrieb verantwortlich ist. Ein neuer digitaler Code wird nur dann im SPI-Modul gespeichert, wenn er zur tatsächlichen maximalen Eingangsspannung gehört.

Die DCMP-Komponente wird verwendet, um aktuelle ADC-Daten mit dem letzten Gewinner (d. h. dem letzten gefundenen Maximum) zu vergleichen, der im SPI-Block gespeichert ist. Es erzeugt einen Impuls am Ausgang OUT+, wenn die neuen ADC-Daten größer als die vorherigen sind. Wir verwenden das OUT+-Signal, um den SPI-Block mit dem neuen Gewinner zu aktualisieren.

Ein globales Taktsignal steuert ADC-Umwandlungen und allgemeine Timings. Sobald eine Konvertierung durchgeführt wurde, pulsiert das INT-Ausgangssignal des ADC zeitlich koordiniert mit dem parallelen Datenausgang des ADC. Wir verwenden den INT-Ausgang auch, um einen 3-Bit-Binärzähler zu inkrementieren, der von DFFs in Matrix1 implementiert wird, was aus drei Gründen nützlich ist:

1. Die Zählerausgangsleitungen adressieren den externen analogen Multiplexer und liefern somit die nächste Eingangsspannung an den ADC;

2. Die Zählung wird in einem 3-Bit-Register (implementiert in Matrix1) eingefroren, um den temporären Gewinner während einer Abtastung zu speichern;

3. Der Zählwert wird decodiert, um ein zweites 3-Bit-Register (implementiert in Matrix0) zu aktualisieren, sobald ein Scan abgeschlossen ist.

Schritt 3: Logikimplementierung

Das ADC-Modul liefert sequentiell die gewandelten Daten aller Eingangsspannungen, einer nach dem anderen, auf unbestimmte Zeit. Sobald der Multiplexer auf 0b111 (dezimal 7) adressiert ist, rollt der Zähler auf 0b000 (dezimal 0) ab, wodurch ein neuer Scan der Eingangsspannungen gestartet wird.

Während des Scans wird das Ausgangssignal ADC INT erzeugt, wenn die parallele Datenausgabe gültig ist. Wenn dieses Signal pulsiert, muss der analoge Multiplexer auf den nächsten Eingang umschalten und den PGA mit der entsprechenden Spannung versorgen. Daher ist der ADC INT-Ausgang das direkte Taktsignal des 3-Bit-Binärzählers von Abbildung 2, dessen paralleles 3-Bit-Ausgangswort direkt den externen analogen Multiplexer anspricht („V select“in Abbildung 1).

Betrachten wir nun ein Beispiel, bei dem die Eingangsspannungen die folgenden Beziehungen haben sollen:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

Abbildung 3 stellt die Hauptsignale dar, die am Max-Decision-Mechanismus beteiligt sind.

Da Daten schließlich synchron mit INT-Impulsen in das SPI-Pufferregister getaktet werden, existiert ein Vergleichsfenster, in dem der SPI-Pufferinhalt mit dem nächsten ADC-Umwandlungsergebnis verglichen wird. Dieses besondere Timing führt zur Erzeugung von OUT+-Impulsen am DCMP-Ausgang. Wir können diese Impulse nutzen, um neue Werte in das SPI-Pufferregister zu laden.

Wie aus der SPI-Puffer-Datenleitung der vorherigen Abbildung hervorgeht, enthält das SPI-Register immer den größten Wert unter den 8 Eingängen und wird nur aktualisiert, wenn vom DCMP-Modul ein größerer Wert erkannt wird (siehe DCMP OUT+-Ausgangslinie des Diagramms, die fehlenden Impulse bewirken, dass V2 im Register verriegelt bleibt, bis es mit V5) verglichen wird.

Schritt 4: Deadlock auflösen

Wenn die implementierte Logik wie oben beschrieben wäre, würden wir natürlich in eine Deadlock-Situation stoßen: Das System ist in der Lage, nur Spannungen zu erkennen, die höher sind als die, die dem im SPI-Pufferregister gespeicherten entsprechen.

Dies gilt auch für den Fall, dass diese Spannung sinken würde und dann ein anderer Eingang, der bisher niedriger war, der höchste wird: er würde nie erkannt. Diese Situation wird in Abbildung 4 besser erklärt, wo nur 3 Eingangsspannungen vorhanden sind Klarheit.

Zum Zeitpunkt von Iteration 2 fällt V3 ab und V1 ist die tatsächliche maximale Spannung. Das DCMP-Modul liefert jedoch keinen Impuls, da die im SPI-Pufferregister gespeicherten Daten (entsprechend 0,6 V) größer sind als die entsprechenden V1 (0,4 V).

Das System verhält sich dann wie ein „absoluter“Max-Finder und aktualisiert die Ausgabe nicht korrekt.

Eine nette Möglichkeit, dieses Problem zu überwinden, besteht darin, das erneute Laden der Daten in das SPI-Pufferregister zu erzwingen, wenn das System einen vollständigen Abfragezyklus aller Kanäle abgeschlossen hat.

Wenn die Spannung an diesem Eingang immer noch am höchsten ist, ändert sich nichts und die Steuerung geht sicher weiter (siehe Abbildung 4 oben, dies ist der Fall der Schleifeniterationen 0 und 1). Wenn andererseits die Spannung an diesem Eingang zufällig auf einen niedrigeren Wert als an einem anderen Eingang absinkt, gibt das erneute Laden des Wertes dem DCMP-Modul die Möglichkeit, beim Vergleich mit dem neuen Maximalwert einen OUT+-Impuls zu erzeugen (dies ist der Fall der Schleifeniterationen 2 und 3).

Ein Stück Logikschaltung ist notwendig, um das Problem zu lösen. Er muss ein Taktsignal an die SPI-Komponente erzeugen, wenn die Schleife den tatsächlichen maximalen Eingang erreicht, wodurch ein erneutes Laden seines aktualisierten Datenworts in das SPI-Pufferregister erzwungen wird. Dies wird in den Abschnitten 7.2 und 7.6 weiter unten besprochen.

Schritt 5: Gerätekonfiguration - Matrix0-Schaltung

Das SLG46620G verfügt über zwei Matrixblöcke, wie in Abbildung 2 dargestellt. Die folgenden Abbildungen zeigen die jeweiligen Gerätekonfigurationen.

Der obere Teil der Schaltung ist das mit 3 DFFs (DFF0, DFF1 und DFF2) realisierte „Loop Register“. Es wird nach jeder Schleife des Eingangsmultiplexers aktualisiert, um an einen 7-Segment-Anzeigentreiber die Binärzahl des „Siegers“, dh des Eingangs mit der höchsten Spannung im letzten Scan, zu senden. Sowohl der Takt zu den DFFs als auch die Daten kommen von der in Matrix1 implementierten Logik über die Ports P12, P13, P14 bzw. P15.

Der untere Teil ist das analoge Frontend mit Eingang an Pin 8 und PGA mit Gain x1. Der Ausgang ADC INT geht sowohl an die Taktlogik von SPI als auch an Matrix1 über Port P0, wo er als Taktsignal für den implementierten Zähler dient.

Die parallelen ADC- und SPI-Datenausgänge sind jeweils mit NET11 und NET15 zum Anschluss an die DCMP-Komponente in Matrix1 gekennzeichnet.

Schritt 6: Gerätekonfiguration - SPI-Taktlogik

Wie bereits im Abschnitt „Logische Implementierung“erwähnt, wird das SPI-Pufferregister jedes Mal aktualisiert, wenn ein Vergleich zwischen dem tatsächlich gespeicherten Wert und den neuen ADC-Wandlungsdaten einen Impuls am Ausgang DCMP OUT+ erzeugt.

Die Signalintegrität ist gewährleistet, wenn dieses Signal mit dem Ausgang ADC INT UND-verknüpft wird. Dies vermeidet jede Spitze und falsche Triggerung.

Wir haben auch unterstrichen, dass zum Überspringen von Deadlock-Situationen der SPI-Puffer aktualisiert werden muss, wenn die Schleife die tatsächlichen Gewinnerdaten erreicht.

Für die richtige SPI-Taktung sind dann drei Signale im Spiel:

1. ADC INT-Ausgang (LUT0-IN1)

2. DCMP OUT+ Ausgang (LUT0-IN0 über Port P10)

3. Anzahl entspricht Latch-Signal (LUT0-IN2 über Port P11)

Die ersten beiden sind UND-verknüpft und beide ODER-verknüpft mit letzterem in LUT0, deren Implementierung wie in Abbildung 6 konfiguriert ist.

Schritt 7: Gerätekonfiguration - Eigenschaften der Matrix0-Komponenten

Die Abbildungen 7-10 zeigen die verbleibenden Eigenschaftsfenster der Komponenten, die zu Matrix0 gehören.

Schritt 8: Gerätekonfiguration - Matrix1-Schaltung

Schritt 9: Gerätekonfiguration - 3-Bit-Binärzähler

Der obere Teil der Schaltung enthält logische Elemente, hauptsächlich einen 3-Bit-Binärzähler, der, wie bereits erwähnt, vom ADC INT-Ausgang getaktet wird. Dieser Zähler ist mit einem ganz „Standard“-Schema implementiert, das in Abbildung 12 dargestellt ist.

Dieser Zähler wird in unserem Design mittels Flip-Flops DFF9, DFF10, DFF11 und INV1, LUT4, LUT8 realisiert. Der DFF9-Ausgang ist das LSB, während DFF11 das MSB ist, wie in Abbildung 13 gezeigt.

LUT4 ist als XOR konfiguriert, während LUT8 die UND-XOR-Logik von Abbildung 12 ausführt.

Zählerausgänge gehen an drei digitale Ausgangspins, um den externen analogen Multiplexer anzusprechen.

LUT10 dekodiert den Code des Zählers, wenn ein Scan abgeschlossen ist und sendet einen Impuls über DLY8 und Port P12 an Matrix0. Dies wird einfach durch UND-Verknüpfen der Ausgänge des Zählers erreicht, wodurch die Zahl 7 dez (0b111 binär, Ende der Schleife) dekodiert wird.

Schritt 10: Gerätekonfiguration - 3-Bit-Vergleichslogik

Abbildung 15 zeigt die Schaltung, die verwendet wird, um zu erkennen, wann die Schleife an der aktuellen „Gewinner“-Adresse iteriert. In diesem Fall sollte, wie bereits erörtert, ein digitaler Impuls ein erneutes Laden des aktuellen ADC-Ergebnisses erzwingen, um eine mögliche Blockiersituation zu lösen.

Die „Gewinner“-Adresse wird im temporären Register von Matrix1 gespeichert (siehe unten), während die aktuelle Adresse vom Binärzähler ausgegeben wird.

XNOR-Gatter liefern einen wahren (logisch 1 oder „hoch“) Ausgang, wenn beide Eingänge gleich sind. Die UND-Verknüpfung dieses Signals für alle Bits (LUT9) gibt uns einen Impuls, wenn beide Binärcodes gleich sind. Details zu XOR-Gattern als Paritätsprüfer finden Sie in der Referenz.

Das „Counter-Equals-Latch“-Signal wird über Port P11 an Matrix0 übergeben.

Schritt 11: Gerätekonfiguration - Digitale Vergleichslogik und temporäres Register

Der untere Teil von Abbildung 11 (hervorgehoben in Abbildung 16) zeigt den DCMP-Block, den Entscheidungsteil dieses Designs.

DFF6, 7 und 8 bilden ein 3-Bit-Register zum Speichern der temporären Eingangsnummer „Gewinner“während die Schleife läuft. Eingabe in die Flip-Flops sind die 3-Bit-Binärzählerausgänge, wie sie in der globalen Matrix1-Schaltung von Fig. 11 sichtbar sind, hier aus Gründen der Klarheit übersprungen.

Ausgänge dieses Registers können die 7-Segment-Anzeige nicht direkt ansteuern, da sich der hier gespeicherte Wert während eines Scans ändert und erst am Ende des Scans selbst als „gültig“betrachtet werden sollte.

Aus diesem Grund sind die temporären Registerausgänge über die Inter-Matrix-Ports P13, P14 und P15 mit dem Loop-Register der Matrix0 verbunden.

Es ist wichtig, in Abbildung 16 zu beachten, dass das temporäre Register vom Ausgang DCMP OUT+ getaktet wird, wenn der Vergleich der ADC-SPI-Register zu einem neuen gefundenen Maximum führt.

Das gleiche OUT+-Signal wird über Port P10 an Matrix0, SPI CLK Logic, weitergegeben.

Schritt 12: Gerätekonfiguration - Eigenschaften der Matrix1-Komponenten

Die Abbildungen 17-19 zeigen die zu Matrix1 gehörenden Komponenteneigenschaftsfenster.

Schritt 13: Ergebnisse

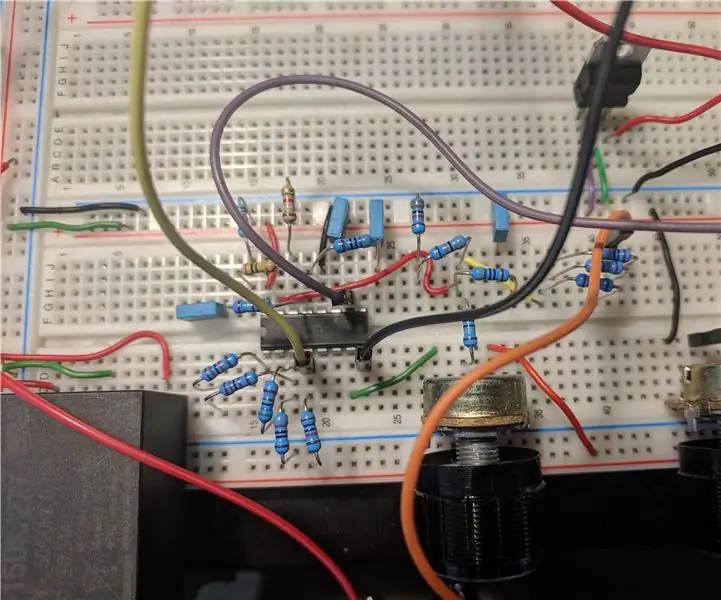

Um die Implementierung zu testen, wurde ein Prototyp des Evaluierungsboards konstruiert, bei dem die 8 analogen Eingangsspannungen durch eine Reihe von Widerstandsteilern mit TrimPots erhalten werden (wie in Abbildung 20 gezeigt).

Der verwendete Multiplexer ist ein ADG508, ein Teil, der mit einer einzigen Versorgung (12 V) betrieben werden kann.

Der 7-Segment-Anzeigentreiber ist ein 74LS47. Es decodiert ein paralleles Eingangswort und steuert direkt eine 7-Segment-Anzeige mit gemeinsamer Anode an.

Das Evaluierungsboard verfügt über einen 2x10 rechtwinkligen Anschluss zum direkten Anschluss an eine GreenPAK Advanced Development Platform an seinem Erweiterungsanschluss, wie in Abbildung 21 gezeigt.

Die Verbindung mit der GreenPAK Advanced Development Platform macht die Messung der Signale für eine schnelle Überprüfung sehr einfach. Abbildung 22 zeigt beispielsweise eine Reihe von Signalen (bzw. CLOCK, ADC INT-Ausgang und DCMP OUT+-Ausgang), wie sie von einem HP 54620A Logikanalysator erfasst wurden. Wellenformen werden durch eine ansteigende Flanke des OUT+-Signals (auf dem Oszilloskop als „A>B“bezeichnet) ausgelöst, daher handelt es sich um eine Wellenformerfassung, wenn eine neue maximale Spannung zwischen den analogen Eingängen erkannt wird. Tatsächlich wurde sie durch Drehen eines der TrimPots des Evaluierungsboards erhalten, um die entsprechende Spannung zu erhöhen, die in Abbildung 22 gezeigt ist.

Abbildung 23 zeigt das Schema des Evaluation Boards.

Abschluss

In diesem Instructable haben wir einen 8-Kanal-Max (oder Min)-Spannungsfinder implementiert, der als gemeinsame Ergänzung zu Mehrkanal-Steuerungssystemen verwendet wird. Der vorgestellte Ansatz nutzt fortschrittliche Funktionen der GreenPAK-Komponenten und zeigt, wie es möglich ist, analoge und digitale Funktionen in einem einzigen Chip zu integrieren. Mehrere kommerzielle ICs können durch Dialog GreenPAKs ersetzt werden, sodass die Anwendungsgröße und die Kosten reduziert werden können.

Empfohlen:

DIY So zeigen Sie die Zeit auf dem M5StickC ESP32 mit Visuino an - Einfach zu tun: 9 Schritte

DIY So zeigen Sie die Zeit auf dem M5StickC ESP32 mit Visuino an - Einfach zu machen: In diesem Tutorial lernen wir, wie Sie den ESP32 M5Stack StickC mit Arduino IDE und Visuino programmieren, um die Zeit auf dem LCD anzuzeigen

Videojuego "Die Geschichte von Max: der kleine Drache": 10 Schritte

Videojuego "Die Geschichte von Max: Der kleine Drache": Si quieres crear el videojuego "Die Geschichte von Max: Der kleine Drache" puedes seguir este paso a paso:

Lass uns bauen (analoger Synth): 5 Schritte

Let's Build (Analog Synth): In dieser Serie zeige ich Ihnen, wie Sie einen einfachen modularen Analogsynthesizer mit analogen und digitalen Komponenten bauen.Link zu Schaltplan und Komponenten: https://drive.google.com/open?id= 1mZX4LyiJwXZLJ3R56SDxloMnk8z07IYJ

Tutorial zum Abtasten analoger Signale - MATLAB: 8 Schritte

Tutorial zum Abtasten analoger Signale | MATLAB: In diesem Tutorial zeigen wir, was Sampling ist. und Wie man ein analoges Signal mit der MATLAB-Software abtastet

Heritage - Keramik im Kontext digitaler und analoger Techniken 2015 – 3 Schritte (mit Bildern)

Heritage - Keramik im Kontext digitaler und analoger Techniken 2015: Keramik war bisher ein Handwerk mit geringem digitalen Einfluss. Aus diesem Grund war es spannend, dieses Handwerk mit einer neuen Technologie zu verbinden. Ausgangspunkt war eine uralte Form und ein CNC Styropor.DESIGNBOOM