Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:15.

- Zuletzt bearbeitet 2025-01-23 12:52.

In der Vergangenheit habe ich eine Anleitung zum Aufbau eines Z80-basierten Computers verfasst und die Schaltung so einfach wie möglich gestaltet, damit sie so einfach wie möglich aufgebaut werden kann. Ich habe auch ein kleines Programm mit der gleichen Idee der Einfachheit geschrieben. Dieses Design funktionierte ziemlich gut, aber ich war nicht ganz zufrieden damit. Ich begann damit, ein Programm dafür umzuschreiben, das es ermöglichte, es während der Laufzeit zu programmieren. Dadurch konnte ich Codestücke testen, ohne sie dem EEPROM widmen zu müssen, was wiederum eine Neuprogrammierung des EEPROMs erfordern würde. Das klang für mich nicht nach einer lustigen Idee. Dann fing ich an, über Speicherräume nachzudenken. Wenn ich ein Stück Hardware (hauptsächlich IO) anbinden wollte, könnte ein Stück Code möglicherweise den für das System verfügbaren Speicherplatz überschreiten. Denken Sie daran, dass das Design nur das untere Byte des Adressbusses verwendet und dann das untere Bit des höheren Bytes verwendet wurde, um zwischen ROM- und RAM-Bereichen auszuwählen. Das bedeutete, dass ich nur 253 Byte Speicherplatz zur Verfügung hatte. Sie fragen sich vielleicht, warum 253 statt 256. Das liegt daran, dass mein neuer Code am Ende eines geschriebenen Programms drei Byte Daten einfügt (dies wird später behandelt, da ich es geändert habe, um an dem neuen Design zu arbeiten).

n

Ich ging meine alten Schaltpläne noch einmal durch, um zu sehen, was sonst noch vor sich ging. Ich habe einen kleinen Fehler bei der Speicherauswahlschaltung gefunden, den ich abdecken werde, wenn ich dort ankomme. Die vereinfachte Version: Alle Schreibanforderungen würden tatsächlich durchlaufen, obwohl sie immer im RAM abgelegt wurden. Das war wahrscheinlich nichts, worüber man sich Sorgen machen sollte, aber dieses Mal wollte ich es richtig machen. Und damit begann ich, einen neuen Schaltplan zu zeichnen. Die beiden Bilder, die dieser Seite beigefügt sind, sind vor und nach der eigentlichen Schaltung. Ich habe so viel von der Spaghetti-Verkabelung aufgeräumt, es ist nicht lustig.

n

Wenn Sie meiner ursprünglichen Vorlage gefolgt sind und planen, dieser zu folgen, werden Sie mich hassen. Wenn Sie neu anfangen, haben Sie Glück. Schnappen Sie sich einfach die Teile in der Liste (oder deren Äquivalent) und folgen Sie ihnen.

Lieferungen:

LM7805 - 5-Volt-ReglerZ80 - die CPU; das Gehirn des SystemsAT28C64B - EEPROM. „Permanenter“Datenspeicher, der für die Firmware des Computers verwendet wird IDT6116SA - SRAM; verwendet zum Speichern von Benutzercode und/oder allgemeiner DatenspeicherungNE555 - Systemuhr74HC374 - Octal D-Latch mit /OE; als Eingangschip verwendet74LS273 - Octal D-Latch mit /MR; AusgangschipTLC59211 - LED-Treiberchip (wird verwendet, damit der 74LS273 LEDs ansteuern kann, da er allein nicht in der Lage ist, die Stromausgabe zu ermöglichen)MC14572 - Dies ist ein "Line Driver" -Chip, aber ich fand ihn perfekt für die Speichersteuerungslogik. Es hat 4 Inverter und ein NAND- und NOR-Gatter, das in 74LS32 eingebaut ist - Quad-OR-GatterCD4001 - Quad-NOR-GatterCD4040 - 12-stufiger Ripple-Zähler; Gezeichneter, aber nicht implementierter Taktteiler (um das System mit langsameren Taktraten zu betreiben)2 10K Ohm-Widerstände - Einer wird in der 555-Timerschaltung verwendet, also verwenden Sie einen beliebigen Wert dafür4 1K Ohm-Widerstände - Einer wird für die 555-Timer-Schaltung, verwenden Sie also, was Sie möchten. Ein anderer wird zum Ansteuern von LEDs verwendet, also variieren Sie ihn auch, wenn Sie möchten8x330 Ohm Resistor Bus8x10K Ohm Resistor Bus11 LEDs - Drei werden für den Systemstatus verwendet und die anderen acht sind Ausgänge. Für die 8 habe ich ein Balkendiagramm verwendet (HDSP-4836) 4 Kondensatoren - Zwei werden beim LM7805 verwendet; 0,22uF und 0,1uF. Einer ist für den 555-Timer, also verwenden Sie, was Sie für richtig halten. Der letzte ist für das Zurücksetzen beim Einschalten; 100uF2 N. O. Drucktasten - Einer wird für die Eingabe verwendet, der andere für Reset8 SPST DIP-Schalter - Dateneingabe; Ich habe Piano Key styleWire verwendet. Viel, viel Draht

n

HINWEIS: Die Durchsteckversion des MC14572 ist veraltet, aber die SMD-Version ist noch aktiv (nicht einmal im Status „Nicht für neues Design“), sodass Sie möglicherweise eine Platine kaufen müssen, um sie verwenden zu können. Anstelle des MC14572 kann ein zweiter 74LS32 verwendet werden (siehe Schema „Speicherauswahlschaltung“der vorherigen Version)

Schritt 1: Schneller Überblick über Änderungen + Schaltpläne

So lesen Sie den Schaltplan:Ein Pfeil, der in einen Chip zeigt, ist ein Eingang:Input >-Ein Pfeil, der von einem Chip weg zeigt, ist ein Output:Output <-Busse verwenden eine Linie anstelle eines Pfeils:Bus |-

n

Die meisten Chips wurden mit ihren genauen Pinbelegungen gezeichnet. Der kleine Dip wurde auf diese Chips gezogen. Die meisten Chips haben auch Pin-Nummern und Etiketten. Sie können etwas schwer zu lesen sein. Mein Bleistift wurde stumpf.

n

In Bezug auf die Schaltungsanschlüsse ist das Layout des neuen Designs gegenüber dem Original weitgehend unverändert. Ich habe das untere Nibble des Adress-High-Bytes mit den Speichern verbunden und dann das Low-Bit des oberen Nibbles (A12) zur RAM/ROM-Auswahl verwendet. Dies bedeutete, dass der ROM-Speicherplatz von 0000-00FF bis zu 0000-0FFF ging. Der RAM-Speicherplatz ging von 0100-01FF auf 1000-1FFF. Ich habe auch die Speichersteuerungslogik für ein besseres Design getauscht und zwei neue Status-LEDs (und etwas Glue-Logik) hinzugefügt. Ich habe auch eine Taktteilerschaltung gezeichnet (aber nicht verdrahtet). Es sollte zwei Funktionen erfüllen. Die offensichtliche Funktion besteht darin, die Taktfrequenz herunterzuteilen. Die andere Funktion ist für PWM-Zwecke (Pulsweitenmodulation) gedacht, da der 555 keine Wellen mit 50% Tastverhältnis erzeugt. Das ist in dieser Schaltung nicht wirklich wichtig, aber wenn Sie die Uhr verwenden möchten, um einige LEDs anzusteuern, werden Sie definitiv die Effekte bemerken (eine (eine Reihe von) LEDs sind dunkler als die andere). Der gesamte Rest der Schaltung ist im Wesentlichen unverändert.

Schritt 2: CPU, Speicher und Speicherkontrolle

Dies ist der Teil, an dem mich die Leser meiner vorherigen Version hassen. Im ursprünglichen Build habe ich einfach Teile auf die Platine geworfen, an einer Stelle, an der sie aussahen, als würden sie beim Verkabeln kein Problem darstellen. Das Ergebnis sah aus, als hätte jemand einen Teller Spaghetti darauf geworfen und war wie "Drähte!" Ich wollte es ein wenig aufräumen, also habe ich damit begonnen, alles außer CPU, RAM und ROM zu zerreißen. Ich habe fast die gesamte Eingangsschaltung, Ausgangsschaltung und die Glue-Logik hochgezogen. Es tat mir fast weh, aber es war notwendig. Ich habe alle Datenverbindungen intakt gelassen und das untere Byte des Adressbusses. Dann habe ich die nächsten vier Bits des Adressbusses (A8-A11) mit dem ROM-Chip verbunden. Ich habe diesmal darauf geachtet, den Chip zu umgehen, um das Hochziehen für die Neuprogrammierung zu erleichtern. Ich habe auch die Adressverbindungen auf den RAM-Chip gesprungen.

n

Nachdem das aus dem Weg war, musste ich jetzt die Speichersteuerlogik verdrahten. Im ursprünglichen Schaltplan hatte ich die /MREQ-Leitung des Prozessors direkt an /CE an beide Speicherchips angeschlossen, dann habe ich /WR an die /WE des RAMs angeschlossen. Dann hatte ich die CPUs /RD und /MREQ logisch ODER zusammen sowie A9. Im Wesentlichen war es so eingerichtet, dass alle Speicheranforderungen sowohl RAM als auch ROM aktivierten, aber A9 wurde verwendet, um auszuwählen, welcher der /OE des Chips ausgewählt wurde. Dies war in Ordnung und alles, weil die Chips inaktiv blieben, bis eine Speicheranforderung gestellt wurde und dann während einer Leseanforderung nur ein /OE aktiv war. Dies verhinderte Übersprechen, führte aber eine unangenehme Nuance ein. Da A9 nur verwendet wurde, um zu bestimmen, welcher Chip Daten ausgab, und da die CPU direkten Zugriff auf den /WE-Pin des RAM hatte, wurden alle Schreibanforderungen durchgeführt. Dies war für das ROM in Ordnung, da sein Schreibmodus verhindert wird, indem /WE direkt an die 5-V-Versorgung angeschlossen wird. Der RAM würde jedoch unabhängig von A9 beschrieben werden. Dies bedeutete, dass ein versuchter Schreibversuch in einen ROM-Speicherplatz an denselben Speicherort im RAM-Speicherplatz schreiben würde.

n

Eine Lösung hierfür wäre, die Steuerlogik so umzuverdrahten, dass die CPU direkten Zugriff auf die /OE- und /WE-Pins der Chips hat, und dann mit MREQ und A12 auszuwählen, welche Chips /CE angesteuert wurden. Ich ging mit dieser Idee, aber anstatt wie das ursprüngliche Design vier NOR-Gatter und einen Inverter zu verwenden, fand ich einen umständlichen kleinen Chip, der perfekt für die Aufgabe war. Ich musste eine Schaltung erstellen, die nur die im Chip verfügbaren Logikgatter verwendet, aber das war einfach genug. A12 speist direkt in ein NAND-Gatter und ein NOR-Gatter ein. /MREQ wird in das NOR-Gatter eingespeist und sein Komplement wird in das NAND-Gatter eingespeist. Das NAND-Gatter wird verwendet, um /CE für den RAM zu treiben, und der NOR-Ausgang wird invertiert und verwendet, um das ROM /CE zu treiben. Dies macht es so, dass /MREQ niedrig sein muss, bevor einer der Chips ausgewählt wird, und dann wählt A12, welcher ausgewählt wird. Mit diesem Setup werden jetzt alle Schreibanforderungen an das ROM nichts tun. Es spart auch Strom, da nur ein Chip aktiv ist, anstatt beide. Was den Logikchip selbst betrifft, haben wir noch zwei ungenutzte Wechselrichter drin. Eine wird sich später gewöhnen, aber wir werden dort ankommen, wenn wir dort sind.

Schritt 3: Systemstatus-LEDs

Bevor ich mit diesem Projekt begann, habe ich versucht, mich mit einem bestimmten IC zu verbinden, aber ich hatte Probleme damit. Ich war mir nicht sicher, was los war, und benutzte eine LED für die Panelmontage, um herumzutasten (eine dieser Baugruppen, die einen eingebauten Widerstand haben). Dadurch kam mir eine Nostalgie-Idee, die noch heute verwendet wird: Status-LEDs zeigten an, ob aus dem Speicher gelesen oder in ihn geschrieben wurde. Es sollte in Verbindung mit der Eingangs-LED verwendet werden, die ich bereits hatte. Die Eingangs-LED wurde mit dem /WAIT-Signalgenerator verbunden, um uns anzuzeigen, dass das System auf Eingaben wartet (ich werde es schaffen, keine Sorge). Ich überlegte, eine LED zur Anzeige eines IO-Schreibens hinzuzufügen, aber ich dachte, dass die Änderung der Ausgangs-LEDs bereits ein guter Indikator dafür wäre. Wenn ich darüber nachdenke, kann ich es noch hinzufügen. Trotzdem finde ich es nützlich zu wissen, ob Speicher gelesen oder geschrieben wird. Nun, es ist auf jeden Fall nützlich für das Debuggen von Programmen. Ich habe es tatsächlich intensiv genutzt, als ich versuchte, mein Programm zum Laufen zu bringen: „Warum schreibt es in den Speicher? Das soll noch nicht passieren!"

n

Um diese LEDs zu steuern, habe ich das Quad-NOR-Gatter verwendet. Ich habe alle Tore benutzt. Nur zwei wurden verwendet, um die Statussignale zu generieren, aber der Chip verfügt nicht über die Leistungsfähigkeit, um die LEDs tatsächlich anzusteuern. Sie sind in der Lage, so viel Leistung zu verbrauchen, daher habe ich die anderen beiden NOR-Gatter als Inverter verwendet und die LEDs als solche angeschlossen. Da eine LED zum Anzeigen von Lesevorgängen und die andere zum Schreiben verwendet wird und eine Lese- und Schreibanforderung nicht gleichzeitig erfolgt, konnte ich nur einen Widerstand für beide LEDs verwenden. Was die Signale angeht, die ich decodieren musste, war das auch einfach genug. Ich wollte, dass alle Speicherleseanforderungen angezeigt werden, also hatte das erste NOR-Gatter /MREQ und /RD an seinen Eingängen. Der Schreibstatus war etwas kniffliger, aber genauso einfach. Ich habe immer noch /MREQ als eine Eingabe verwendet, aber die Verwendung von /WR als die andere würde eine kleine Nuance verursachen, die ich vermeiden wollte. Es hätte ALLE Schreibanforderungen angezeigt. Ich wollte nur die, die tatsächlich durchgegangen sind. Also wie würde ich das machen? Erinnern Sie sich, wie ich das System eingerichtet habe, damit nur der RAM geschrieben werden kann? Ich habe die RAMs /CE als anderen Eingang zum NOR-Gatter verwendet. Das bedeutet, dass die LED nur leuchtet, wenn RAM ausgewählt ist und eine Schreibanforderung gestellt wird. In Bezug auf die LED-Farbe habe ich Orange als Leseanzeige gewählt (ich habe aber nur gelbe gefunden) und Rot als Schreibanzeige.

Schritt 4: Eingabe und Ausgabe

Im vorherigen Schritt haben Sie vielleicht bemerkt, dass ich der Platine bereits einige der restlichen Komponenten hinzugefügt habe. Ich habe den Platz reserviert, damit ich nicht versehentlich Drähte dort platzieren konnte, wo ich eine Komponente haben wollte (also musste ich einen neuen Ort für diese Komponente finden). Sie haben vielleicht auch bemerkt, dass ich die Eingangsschalter an Ort und Stelle gelassen und mit der Stromschiene verdrahtet habe. Ich entschied, dass der ursprüngliche Standort der perfekte Ort war und beschloss, die Ausgangs-LEDs in der Nähe (oben) zu platzieren. Rechts neben der Balkenanzeige befindet sich das Eingabelatch. Darüber befindet sich der Ausgangs-Latch und links davon der LED-Treiber. Ich begann damit, das Display mit dem Treiber zu verbinden, da dies am einfachsten war. Dann habe ich die Schalter an die Eingangsseite des Eingangslatchs angeschlossen. Als nächstes verband ich die Ausgangsseite des Ausgangslatchs mit dem LED-Treiber. Dies mag wie eine umständliche Anordnung erscheinen, diese zu verkabeln, aber es hatte einen Grund. Der Eingang des Ausgangslatchs sollte ebenso mit dem Datenbus verbunden werden wie der Ausgang des Eingangslatchs. Die Idee war, die Ausgänge des Eingangslatchs mit den Eingängen des Ausgangslatchs zu verbinden, was ich getan habe. Dann musste ich nur noch dieses Chaos an den Datenbus anschließen. Es spielte keine Rolle, wohin diese Verbindungen physisch gingen, da sie alle elektrisch verbunden waren. Der Computer ist jetzt fast fertig.

Schritt 5: Eingabe und Ausgabe zurücksetzen und beenden

Entschuldigung, keine Bilder für diesen Schritt. Siehe den vorherigen Schritt für die Bilder.

n

Sie haben vielleicht im letzten Bild des vorherigen Schrittes bemerkt, dass ich einen grünen Knopf und einen anderen Logikchip installiert hatte. Der Chip ist das ODER-Gatter. Zwei Gatter werden verwendet, um das /WAIT-Signal zu erzeugen. Nun, man erzeugt das Signal durch ODER-Verknüpfung von /IORQ und /RD vom Prozessor. Der Ausgang wird in das zweite Gate eingespeist, wo er erneut mit einem Taster ODER-verknüpft wird. Die Taste bringt den Eingang des Gates auf High und damit den Ausgang auf High. Dieser Ausgang wird dem /WAIT-Pin des Prozessors zugeführt. Solange er nicht gedrückt ist, hält ein Widerstand den Eingang niedrig. Ich habe anfangs einen 10K-Widerstand verwendet, aber der LS32 hat tatsächlich Spannung am Eingang ausgegeben. Der Widerstand hat ihn nicht tief genug fallen lassen und ich musste ihn durch einen 1K ersetzen. Wie auch immer, die Idee ist, dass, wenn eine E/A-Leseanforderung gestellt wird, das erste und das zweite ODER-Gatter dem Prozessor sagen, dass er warten soll. Sobald Sie die Eingangsschalter auf den gewünschten Wert eingestellt haben, drücken Sie die Taste und die CPU wird aus dem Wartezustand geholt. Die grüne „Eingangs“-LED, wie ich sie in einem früheren Schritt genannt habe, ist so verdrahtet, dass sie aufleuchtet, wenn der /WAIT-Pin auf Low geht.

n

Aber wir sind noch lange nicht fertig. Das Eingangs-Flipflop benötigt ein Signal, um mitzuteilen, wann die Dateneingabe gültig ist und an die CPU ausgegeben werden soll. Dieser Takt-Pin ist aktiv hoch. Vorher haben wir es nur mit der Taste verbunden. Dies ist immer noch eine gültige Option, aber dieses Mal habe ich mich dafür entschieden, sie auf denselben Ausgang wie das zweite ODER-Gatter zu legen. Dieser IC hat auch einen /OE-Pin, der angesteuert werden muss. Wenn er hoch gehalten würde, würde er niemals Daten in den Bus einfügen. Wenn es niedrig gehalten wurde, würde es immer den Bus fahren. Um dies zu beheben, habe ich einfach ein drittes ODER-Gatter verwendet. Die Eingänge sind /IORQ und /RD und der Ausgang geht direkt zum /OE des Latch.

n

Der Ausgangs-Latch muss auch den Takt-Pin ansteuern. Auch hier ist es aktiv hoch. In meinem Schaltplan habe ich das vierte ODER-Gatter gezeichnet, das den Pin direkt mit /IORQ und /WR ansteuert. Dies bedeutete, dass der Clock-Pin hoch gehalten wurde, bis eine Schreibanforderung gestellt wurde, dann würde er niedrig und dann wieder hoch gehen. Dies wäre wahrscheinlich in Ordnung gewesen, da der Datenbus unmittelbar nach dem Schreibversuch noch gültige Daten hatte, aber aus technischer Sicht war es ein Mülldesign. Ich habe diesen Fehler erst bemerkt, nachdem ich die letzten Bilder gemacht hatte, aber ich habe diese Verbindung zerrissen und dann den ODER-Gatter-Ausgang in einen der unbenutzten Inverter von der Speichersteuerlogik eingespeist und dann seinen Ausgang mit dem Taktstift verbunden. Ich habe auch den Schaltplan repariert und einen anderen Fehler gefunden, den ich gemacht hatte. Ich habe es auch korrigiert.

n

Nachdem das alles endlich erledigt war, hatte ich nur noch sehr wenig Arbeit zu tun: die Reset-Schaltung. Ich habe der Platine einen Knopf hinzugefügt und einen 10K-Widerstand verwendet, um eine Seite hoch zu halten. Die andere Seite geht direkt auf Masse. Die hochgehaltene Seite ist der /RESET-Ausgang, der mit einem /RESET-Pin an jeden Chip ging (die CPU und das Ausgangslatch). Um das Zurücksetzen beim Einschalten durchzuführen, habe ich dem /RESET-Ausgang einen Kondensator hinzugefügt. Die Idee ist, dass der Widerstand mit großem Wert dazu führen würde, dass sich der relativ große Kondensator langsam auflädt und die /RESET-Pins für einige Taktzyklen niedrig hält (die CPU benötigt vier Taktzyklen). Sie können wahrscheinlich bereits erraten, was die negative Seite dieser Schaltung ist. Es ist das gleiche Negativ wie die vorherige Version, weil es die gleiche Schaltung ist. Wenn die Taste gedrückt wird, wird der Kondensator im Wesentlichen durch die Taste kurzgeschlossen. Dies ist sowohl für die Kappe als auch für die Schaltfläche schlecht. Wenn Sie also Ihren Build ein wenig dauerhafter gestalten möchten, möchten Sie ihn möglicherweise neu gestalten. Ich dachte an einen anderen 555-Timer, der im monostabilen Modus eingerichtet wurde. Aber damit ist die Computerschaltung nun fertig. Yay. Jetzt muss es programmiert werden.

Schritt 6: Programmierung

Dieses Ding zu programmieren war ein Albtraum. Ich habe einen Arduino EEPROM-Programmierer gebaut. Es hat nicht funktioniert. Ich baute einen anderen basierend auf dem Design und der Codierung eines anderen. Hat trotzdem nicht funktioniert. Ich kehrte zu der bewährten Methode zurück, die Adressen und Datenbytes manuell von Hand zu setzen. Irgendwie habe ich das vermasselt. Ich habe es noch einmal versucht und es ist immer noch falsch. Ich ging noch einmal zurück und stellte fest, dass es um ein einziges Byte daneben war, also korrigierte ich es und es funktionierte endlich, Gott sei Dank.

n

Das eigentliche Programm sieht so aus, als wäre es super komplex und schwer zu befolgen, aber das ist es nicht. Es ist eigentlich ganz einfach. Die Hälfte davon ist das Kopieren von Zahlen. Die andere Hälfte teilen sich 16-Bit-Mathematik, bedingte Sprünge und noch mehr Kopieren von Zahlen. Also lassen Sie mich es durchgehen und Ihnen sagen, wie es funktioniert.

n

Die Initialisierung setzt nur einige Registerwerte zur Verwendung durch das Programm. Die Programmschleife ist etwas komplexer, aber nicht viel. Zuerst akzeptiert es Eingaben in das A-Register an Port 00. Dann wird das E-Register in den Speicher geschrieben. In den ersten beiden Schleifen enthält das E-Register Junk-Daten, daher versuchen wir, sie in die letzten beiden Bytes des ROM-Speichers zu schreiben, da sie nicht wirklich geschrieben werden; der Adresszeiger (IY) wird dann inkrementiert. Der in D gespeicherte Wert wird dann in E verschoben, um als nächstes geschrieben zu werden. Dann wird A in D und L geladen und E in H kopiert. In HL erfolgt der Wertevergleich durch Subtraktion und Überprüfung von ZF (Nullflag). Der erste verglichene Wert wird in den Registern B und C gespeichert. B und C werden als ein einzelnes 16-Bit-Register BC behandelt. Wenn die Werte gleich sind, springt das Programm direkt in den RAM-Speicher, wo angenommen wird, dass sich der Benutzercode befindet. Wenn der Code in BC nicht übereinstimmt, wird HL mit den Anfangswerten von D und E neu geladen und erneut mit dem Wert in SP auf die gleiche Weise verglichen, wie er mit BC verglichen wurde. Wenn es eine Übereinstimmung ist, hat es das gleiche Ergebnis, aber drei zusätzliche Bytes werden in den Speicher geschrieben. Die Bytes sind ein Code, der die CPU veranlasst, an den Anfang ihres Programms zurückzuspringen (ein Software-Reset). Wenn der zweite Vergleich jedoch nicht übereinstimmt, springt das Programm dorthin, wo es einen Wert vom Benutzer abruft.

n

LDSP, EDBFH; exe-Code (fügt Sprung hinzu)

n

LD IY, FFEH; initialer Speicherzeiger für Codespeicherung

n

LDBC, EDC3H; exe-Code (keine Schleife)

n

Schleife; Assembler-Direktive, damit wir nicht wissen müssen, wo sich dieser Teil im Speicher befindet

n

EIN, (00H); Programmdaten abrufen

n

LD (IY+00H), E; E enthält zu speichernden Code

n

INC IY; zum nächsten Speicherplatz wechseln

n

LD E, D; ld D in E

n

LD D, A; ld A in D

n

LDH, E; ld E in H

n

LD L, D; ld D in L

n

ODER EIN; Carry-Flag zurücksetzen

n

SBC HL, BC; gibt 0 zurück, wenn exe-Code 2 eingegeben wurde

n

JPZ, 1000H; Wenn ja, zum Programm springen und es ausführen

n

LDH, E; andernfalls aktualisieren Sie diese auf die richtigen Werte

n

LD L, D

n

ODER EIN; die erste Subtraktion kann das Übertragsflag gesetzt haben. Löschen Sie es

n

SBC HL, SP; gibt 0 zurück, wenn exe-Code 1 eingegeben wurde

n

JP NZ, Schleife; wenn nicht, Vorgang wiederholen (beginnend mit dem Abrufen eines Wertes)

n

LD (IY+00H), C3H; andernfalls fügen Sie einen Sprungcode am Ende des Benutzerprogramms ein

n

LD (IY+01H), 00H; jump wirkt im Grunde wie ein Software-Reset

n

LD (IY+02H), 00H; Es ist ein vollständiger Reset, falls Register geändert wurden

n

JP 1000H; zum Anwenderprogramm springen und ausführen

Empfohlen:

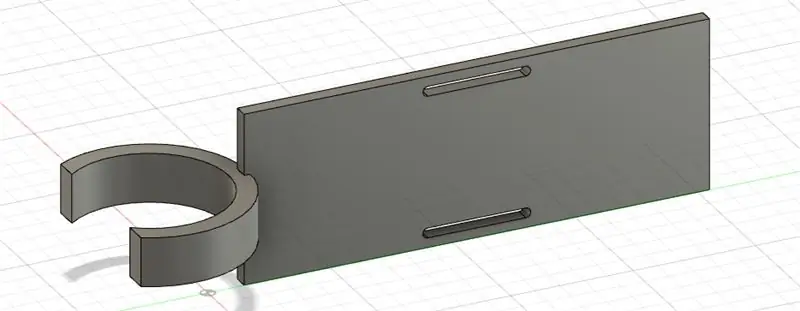

Entwicklung des Drivemall-Boards: 5 Schritte

Entwicklung des Drivemall Boards: In diesem Tutorial sehen wir die grundlegenden Schritte zum Erstellen eines benutzerdefinierten Arduino-Boards. Die verwendete Software ist KiCad für das Boarddesign und die Arduino IDE für das Erstellen und Laden der Firmware für das Board

Installieren des Windows-Subsystems für Linux (WSL): 3 Schritte

Installieren des Windows-Subsystems für Linux (WSL): Diese Anleitung soll Benutzern helfen, das Windows-Subsystem für Linux auf ihrem Windows 10-Computer zu installieren. Die spezifische Linux-Distribution, die dieser Befehlssatz verwendet, heißt Ubuntu. Schauen Sie hier für eine Übersicht über die verschiedenen Linux

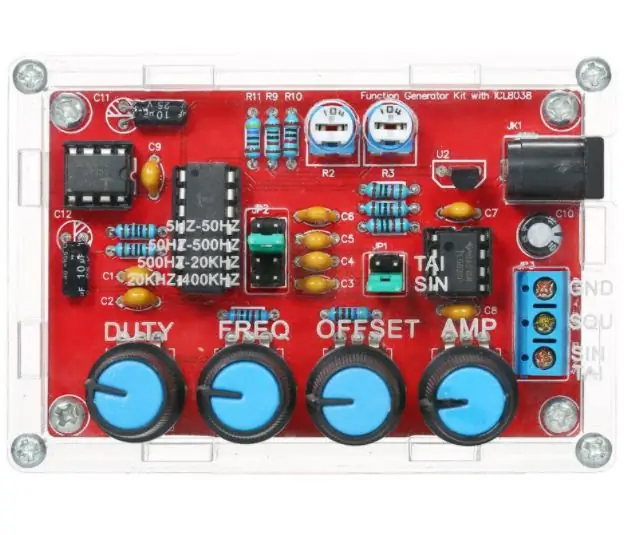

Kennenlernen des "Professional ILC8038 Function Generator DIY Kit": 5 Schritte

Kennenlernen des "Professional ILC8038 Function Generator DIY Kit": Auf der Suche nach neuen Elektronikprojekten bin ich auf ein süßes kleines Funktionsgenerator-Kit gestoßen. Es wird als „Professional ILC8038 Function Generator Sine Triangle Square Wave DIY Kit“bezeichnet und ist bei einer Reihe von Anbietern erhältlich

Überprüfung des JDM-Programmierers: 9 Schritte

JDM Programmer Review: JDM ist ein beliebter PIC-Programmierer, da er einen seriellen Port, ein Minimum an Komponenten und keine Stromversorgung verwendet. Aber es gibt Verwirrung da draußen, mit vielen Programmiervarianten im Netz, welche funktionieren mit welchen PICs? In diesem „Instru

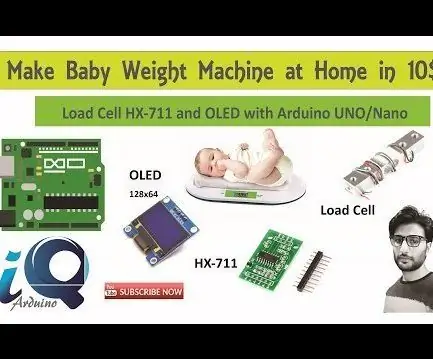

Wie man eine Babygewichtsmaschine mit Arduino Nano, HX-711 Wägezelle und OLED 128X64 herstellt -- Kalibrierung des HX-711: 5 Schritte

Wie man eine Babygewichtsmaschine mit Arduino Nano, HX-711-Wägezelle und OLED 128X64 herstellt || Kalibrierung von HX-711: Hallo Instructables, vor wenigen Tagen wurde ich Vater eines süßen Babys?. Als ich im Krankenhaus war, stellte ich fest, dass das Gewicht des Babys so wichtig ist, um das Wachstum des Babys zu überwachen. Also ich habe eine Idee? um eine Babygewichtsmaschine von meinem Selbst zu machen. In diesem Instructable ich