Inhaltsverzeichnis:

- Lieferungen

- Schritt 1: Anforderungen an die serielle Schnittstelle

- Schritt 2: PIC-Programmieranforderungen

- Schritt 3: JDM-Spezifikation

- Schritt 4: Schaltungsbeschreibung

- Schritt 5: Vorbereitung auf die Simulation

- Schritt 6: Änderungen für ICSP

- Schritt 7: Simulationsergebnisse

- Schritt 8: Schlussfolgerungen

- Schritt 9: Und schließlich

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:15.

- Zuletzt bearbeitet 2025-06-01 06:08.

JDM ist ein beliebter PIC-Programmierer, da er einen seriellen Port, ein Minimum an Komponenten und keine Stromversorgung verwendet. Aber es gibt Verwirrung da draußen, mit vielen Programmiervarianten im Netz, welche funktionieren mit welchen PICs? In diesem "instructable" haben wir JDM auf die Probe gestellt und ich demonstriere, wie man die Schaltung mit Spice simuliert, die alle Ihre Fragen beantwortet!

Lieferungen

LTspice, das hier von Analog Devices heruntergeladen werden kann.

Sie benötigen hier auch die JDM-Schaltungsdateien.

Schritt 1: Anforderungen an die serielle Schnittstelle

JDM erfordert eine serielle Schnittstelle, die der EIA232-Spezifikation entspricht, idealerweise mit +12/-12 Spannungspegeln.

Laut Datenblatt des Texas Instruments Line Driver MC1488 (Abbildung 3)

Ausgangsimpedanz = 4V/8mA = 500 Ohm.

Kurzschlussstrombegrenzung = 12 mV, ohne Zeitbegrenzung - keine Beschädigung des Chips.

Eingangsimpedanz des Leitungsempfängers = 3k bis 7k Ohm empfohlen.

Serielle Ports auf älteren Desktop-PCs verwenden +12 V/-12 V, um diese Anforderung zu erfüllen.

Serielle Anschlüsse an neueren Laptop-PCs verwenden niedrigere Spannungen. JDM kann funktionieren oder auch nicht - die Antwort ist komplexer.

Schritt 2: PIC-Programmieranforderungen

Informationen zu den PIC-Programmieranforderungen erhalten Sie von Microchip. Das obige gilt für ein typisches Gerät.

Schritt 3: JDM-Spezifikation

Ist die ursprüngliche JDM-Website im Laufe der Zeit verloren gegangen? Dies lässt uns raten, was der Designer ursprünglich für die Spezifikation beabsichtigt hatte.

- Stellen Sie VDD=5V und bis zu IDD=2mA maximal bereit (für „In-Socket“-Version)

- Stellen Sie VHH = 13 V und bis zu IHH = 0,2 mA maximal bereit.

- MCLR Anstiegszeit tVHHR = 1uS max.

- Die ICSP-Version muss in der Lage sein, MCLR gegen 22k-Pull-up auf dem Ziel niedrig zu ziehen.

Schritt 4: Schaltungsbeschreibung

Abbildung JDM1 basiert auf der „Standard“-JDM-Schaltung von der PICPgm-Website. Dies ist der „PIC in Socket“-Programmierer, bei dem PIC Strom von TX- und RTS-Pins bezieht. Das ursprüngliche Diagramm war schwer zu verstehen, daher habe ich es mit der normalen Konvention des Stromflusses von oben nach unten neu gezeichnet. Und ich habe LED-Anzeigen „RESET“, „PROG“und „RTS“hinzugefügt, die während des Aufbaus und Testens notwendig sind. Hoffentlich haben diese keine nachteiligen Auswirkungen auf das Verhalten.

Die normale Konvention beim Schaltungsdesign besteht darin, alle Erdungen gemeinsam zu verwenden, aber das Hauptmerkmal von JDM besteht darin, dass die Masse des seriellen Anschlusses (GND) mit VDD verbunden ist. Dies führt zu Verwirrung, da serielle Portsignale in Bezug auf GND und PIC-Signale in Bezug auf logische Masse (VSS) gemessen werden.

Wenn TX hoch geht, verhält sich Q1 wie zwei in Durchlassrichtung vorgespannte Dioden. (Der Kollektor von Q1 ist nicht wie beim normalen Transistorbetrieb in Sperrrichtung vorgespannt). Der Kollektor von Q1 lädt C2, das durch Zener (D3) auf VDD+8V geklemmt wird. Der Q1-Emitter liefert 13 V an MCLR für den Programmier-/Verifizierungsmodus.

Wenn TX niedrig wird, wird der Kondensator C3 über D1 geladen und VSS wird durch Zener (D5) auf VDD-5 V geklemmt. Auch TX wird bei (VSS-0.6) von D1 geklemmt. Q1 ist ausgeschaltet, C1 hält seine Ladung für den nächsten Programmierimpuls. MCLR wird von D2 auf 0 V geklemmt, sodass der PIC jetzt zurückgesetzt ist.

Wenn RTS hoch ist, wird der Takt an PGC gesendet. D4 klemmt PGC bei VDD logisch hoch. Wenn RTS niedrig ist, wird der Kondensator C3 über D6 geladen und VSS wird durch Zener (D5) auf VDD-5 V geklemmt. D6 klemmt PGC auf VSS oder logisch 0.

Während der Programmierung werden auf DTR gesendete Daten auf PGD gelesen, die der PIC als Eingang konfiguriert. Wenn DTR hoch ist, fungiert Q2 als „Emitterfolger“und die PGD-Spannung beträgt ungefähr (VDD-0.6) oder logisch 1. Wenn DTR niedrig ist, wirkt Q2 als fehlerhafter Transistor (Emitter- und Kollektorpins vertauscht). Q2 zieht PGD auf Low, das von D7 bei VSS oder logisch 0 geklemmt wird.

Während der Überprüfung konfiguriert der PIC PGD als Ausgang zum Senden von Daten an den seriellen Port. DTR muss hoch eingestellt sein und Daten werden auf CTS gelesen. Wenn der PGD-Ausgang hoch ist, ist Q2 ausgeschaltet, CTS = DTR = +12 V. Wenn der PGD-Ausgang niedrig ist, ist Q2 eingeschaltet. Der Kollektor von Q2 zieht Strom (12 V + 5 V) / (1k + 1k5) = 7 mA vom DTR und zieht CTS auf VSS.

Schritt 5: Vorbereitung auf die Simulation

Laden Sie LT Spice herunter, speichern und öffnen Sie die hier bereitgestellten Schaltungsdateien (*.asc). Um die Schaltung zu simulieren, müssen wir ihr einige Eingänge geben und dann die Ausgänge „verfolgen“. V1, V2 V3 simulieren den seriellen 12-V-Port mit der Ausgangsimpedanz R11, R12, R13.

- V1 erzeugt 2 Programmimpulse auf TX von 0,5 ms bis 4,5 ms

- V2 erzeugt Datenimpulse auf DTR von 1,5 bis 4,5 ms

- V3 erzeugt Taktimpulse auf RTS von 0,5 bis 3,5 ms

Die Komponenten V4, X1, R15 und R16 sind alle Bestandteil der Simulation.

- V4 erzeugt 2 Impulse von 2,5 bis 4,5 ms zum Verifizieren von Daten.

- Jumper X1 simuliert AUSGANG auf PGD.

- R15, R16 simulieren das „Laden“von PIC auf VDD und MCLR.

Schritt 6: Änderungen für ICSP

Abbildung JDM3 zeigt die Version für die „In Circuit“-Programmierung. Änderungen vom Original sind

- ZIF-Buchse durch ICSP-Stecker ersetzen.

- Der PIC wird nun durch die Versorgung der Zielschaltung (V5) mit Strom versorgt.

- 5V-Zener (D5) entfernen.

- Der kleine 100pF-Kondensator (C4) wird neben dem PIC auf der Zielschaltung verschoben.

- LEDs beziehen Strom von der Platine, wenn möglich.

- Der MCLR-Pull-up-Widerstand (R10) und die Diode (D10) sind auf der Zielschaltung erforderlich.

- WARNUNG. Das Zielboard muss eine „schwimmende“Versorgung haben, idealerweise eine Batterie.

- Verbinden Sie die Zielmasse (VSS) nicht mit der Computer-/PC-Masse, indem Sie gleichzeitig mit JDM andere Computeranschlüsse anschließen.

Nach der Simulation von JDM1 wurde das Problem der langen Ladezeit auf C2 offensichtlich. Nach dem Lesen von Fruttenboel scheint es dann, dass C2 und Q1 als Modifikation zum Original hinzugefügt wurden. Ich kann mir nicht vorstellen, was C2 und Q1 bewirken sollen, außer Probleme zu verursachen. Für JDM4 greifen wir also auf das ältere Design von Fruttenboel zurück, das einfach und unkompliziert zu verstehen ist. D1 und D3/LED2 klemmen MCLR zwischen VSS und VDD+8V. Der Wert von R1 wird auf 3k3 reduziert, gerade ausreichend, um LED2 mit 12V zu beleuchten.

JDM4 ist auch für schwächere serielle Ports ausgelegt. Wenn TX hoch wird (+9V), TX-Stromquelle = (9-8)/(1k +3k3) = 0,2 mA, gerade genug, um MCLR hoch zu ziehen, obwohl es nicht ausreicht, um LED2 zu beleuchten. Wenn TX niedrig wird (etwa -7 V), TX-Stromsenke = (9-7) / 1k = 2 mA. LED1 Strom = (7-2 für LED)/(2k7) = 1,8mA. MCLR-Pulldown-Strom = 7-5,5/3k3 = 0,5mA.

Diese Schaltung wurde auch getestet (JDM5-Simulation), um zu sehen, was mit seriellen Ports von mindestens +/-7 V passiert, wenn nicht genügend Spannung vorhanden ist, um VHH = 13 V aufrechtzuerhalten. Der Zweck von C1 wird jetzt offensichtlich, C1 erzeugt einen kurzen +ve-Boost für MCLR, eine 33us-Spitze an der steigenden Flanke von TX, ausreichend lang genug, damit der PIC vielleicht in den Programmiermodus wechselt? Entfernen Sie jedoch Jumper X2 (deaktivieren Sie LED1), da nicht genügend Strom vorhanden ist, um MCLR nach unten zu ziehen und LED1 zusammen zu leuchten. Wenn TX niedrig wird, TX-Stromsenke = (7V-5,5V)/(1k+3k3) = 0,3mA, gerade ausreichend, um MCLR gegen den Pull-up-R10 niedrig zu ziehen.

Schritt 7: Simulationsergebnisse

Um die Grafikdateien anzuzeigen, ist es besser, mit der rechten Maustaste auf die untenstehenden Links zu klicken und dann "Link in neuem Tab öffnen" auszuwählen.

Simulation 1: Trace von MCLR, VSS und RTS für Original-JDM1. Sofort fallen die Beobachtungen 1, 2 und 3 ins Auge.

Simulation 2: Trace von MCLR und VSS sowie RTS für modifiziertes JDM2, das frühere Probleme behebt.

Simulation 3: Trace von PGD, VSS und PGC für JDM2 beim Senden von Daten im Programmmodus. Beobachtung 4 bei 3,5 mS.

Simulation 4: Trace von PGD, VSS und CTS für JDM2 im Verifizierungsmodus (Jumper X1 gesteckt). OK

Simulation 5: Trace von MCLR, VSS, PGD und PGC für JDM3. ICSP, das Strom von der Schaltung verwendet, löst viele Probleme.

Simulation 6: Trace von MCLR, VSS, PGD und PGC für JDM4 mit +/-9V serieller Schnittstelle. MCLR fährt sofort hoch, voll funktionsfähig.

Simulation 7: Trace von MCLR, VSS und TX für JDM5 mit +/-7V serieller Schnittstelle und entferntem Jumper X2. C1 erzeugt einen +ve-Boost (Spike) an der steigenden Flanke von MCLR, der gerade ausreicht, um MCLR über TX auf 13 V zu drücken.

Schritt 8: Schlussfolgerungen

Spice ist wirklich gut darin, „versteckte Geheimnisse“des Schaltungsbetriebs zu enthüllen. Offensichtlich funktioniert die JDM-Schaltung und ist mit vielen PIC-Chips kompatibel, aber die folgenden Beobachtungen zeigen mögliche Einschränkungen/Kompatibilitätsprobleme/Fehler auf?

- Lange Anstiegszeit von MCLR, während C2 beim ersten Impuls von TX auf VPP geladen wird. Verfehlt Spezifikation 3.

- Der serielle Port lädt C2, wenn TX hoch und RTS niedrig wird. RTS hat aber auch die Aufgabe, C3 aufzuladen. Wenn beides gleichzeitig auftritt, führt dies zu einer höheren Belastung des RTS, folglich verliert C3 bei der Simulation nach 2 ms Ladung (VSS steigt). Verfehlt Spezifikation 1.

- C3 verliert Ladung (VSS beginnt zu steigen), nachdem die Taktimpulse bei 3,5 ms stoppen.

- Was ist der Zweck von C2, wird es überhaupt benötigt?

Lösungen

- Vermutlich verwendet PICPgm einen Software-„Workaround“. Es muss einen langen TX-Impuls anlegen, um C2 vorzuladen, und dann erst nach dem zweiten TX-Impuls in den Programmiermodus wechseln? Für die Simulation habe ich den Wert von C2 auf 1uF reduziert, um eine Anstiegszeit von 1ms zu erhalten. Keine ideale Lösung.

- Teilen Sie C2 und C3 auf, damit sie unabhängig voneinander aufgeladen werden. Eine kleine Modifikation von JDM2, C2, bezieht sich auf GND anstelle von VSS.

- Gelöst von JDM3. ICSP ist viel zuverlässiger, da PIC von der Zielschaltung gespeist wird.

- JDM4 löst Problem 1. Dies ist ein einfaches Design, das C2 vollständig eliminiert.

Schritt 9: Und schließlich

Der Beweis für den Pudding liegt im Essen. Dieses JDM funktioniert, also verwenden Sie es weiter.

Und meine Empfehlungen sind:

- Verwenden Sie JDM2 für die In-Socket-Programmierung und serielle 12-V-Ports,

- Verwenden Sie JDM4 für ICSP-Programmierer und serielle Ports über +/-9V,

- Verwenden Sie JDM4 mit entferntem Jumper X2 für serielle Ports über +/-7V.

Verweise:

Analog Devices LT Gewürz

picpgm

Fruttenboel

Verfolgen Sie weitere PIC-Projekte bei sly-corner

Empfohlen:

Erste Schritte mit Amara: 7 Schritte

Erste Schritte mit Amara: Amara ist ein kostenloser Untertitel-Editor, mit dem Sie ganz einfach Untertitel zu Videos hinzufügen können – vom Unterricht bis zum persönlichen Gebrauch. Diese Anweisungen helfen Ihnen, ein Amara-Konto einzurichten, damit Sie schnell und einfach Untertitel hinzufügen können

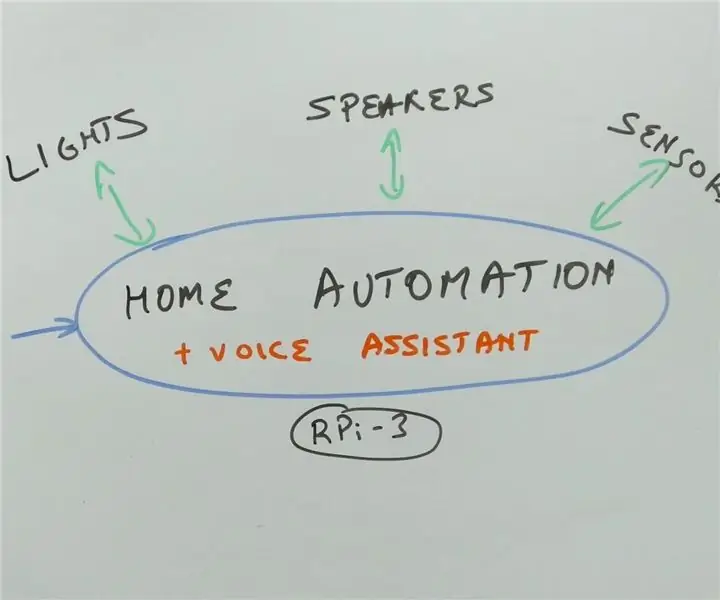

Erste Schritte mit der Heimautomatisierung: Home Assistant installieren: 3 Schritte

Erste Schritte mit der Hausautomation: Home Assistant installieren: Wir starten jetzt die Hausautomationsserie, in der wir ein Smart Home erstellen, das es uns ermöglicht, Dinge wie Licht, Lautsprecher, Sensoren usw. über einen zentralen Hub zusammen mit einem Sprachassistent. In diesem Beitrag erfahren Sie, wie Sie in

Erste Schritte mit dem SkiiiD-Editor: 11 Schritte

Erste Schritte mit dem SkiiiD-Editor: skiiiD-Editor, Entwicklungsboard-Firmware IDEskiiiD-Editor basiert auf skiiiD (Firmware Development Engine). Jetzt ist es mit Arduino UNO, MEGA und NANO mit 70+ Komponenten kompatibel.BetriebssystemmacOS / WindowsInstallierenBesuchen Sie die Website https:

Erste Schritte mit Python: 7 Schritte (mit Bildern)

Erste Schritte mit Python: Programmieren ist großartig! Es ist kreativ, macht Spaß und gibt Ihrem Gehirn ein mentales Training. Viele von uns wollen etwas über Programmieren lernen, aber überzeugen sich selbst davon, dass wir es nicht können. Vielleicht hat es zu viel Mathematik, vielleicht der Jargon, der erschreckend herumgeworfen wird

Raspbian in Raspberry Pi 3 B ohne HDMI installieren - Erste Schritte mit Raspberry Pi 3B - Einrichten Ihres Raspberry Pi 3: 6 Schritte

Raspbian in Raspberry Pi 3 B ohne HDMI installieren | Erste Schritte mit Raspberry Pi 3B | Einrichten Ihres Raspberry Pi 3: Wie einige von Ihnen wissen, sind Raspberry Pi-Computer ziemlich großartig und Sie können den gesamten Computer nur auf einer einzigen winzigen Platine bekommen. Das Raspberry Pi 3 Model B verfügt über einen Quad-Core 64-Bit ARM Cortex A53 mit 1,2 GHz getaktet. Damit ist der Pi 3 ungefähr 50