Inhaltsverzeichnis:

- Schritt 1: Benutzerbedienung des digitalen Sequenzers

- Schritt 2: Technische Details

- Schritt 3: Technische Details

- Schritt 4: 7-Segment-Taktteiler

- Schritt 5: Beats Per Minute Clock Divider

- Schritt 6: Tonhöhentaktteiler

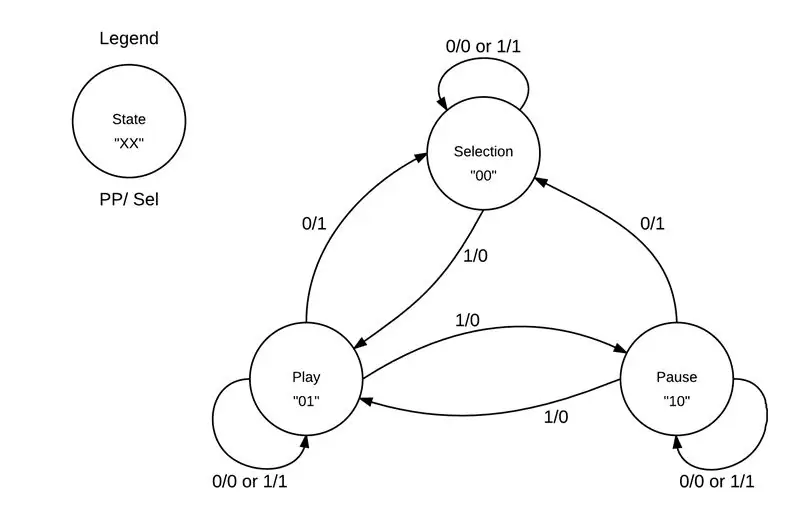

- Schritt 7: Play/Pause/Select State Machine

- Schritt 8: Play/Pause/Select State Machine

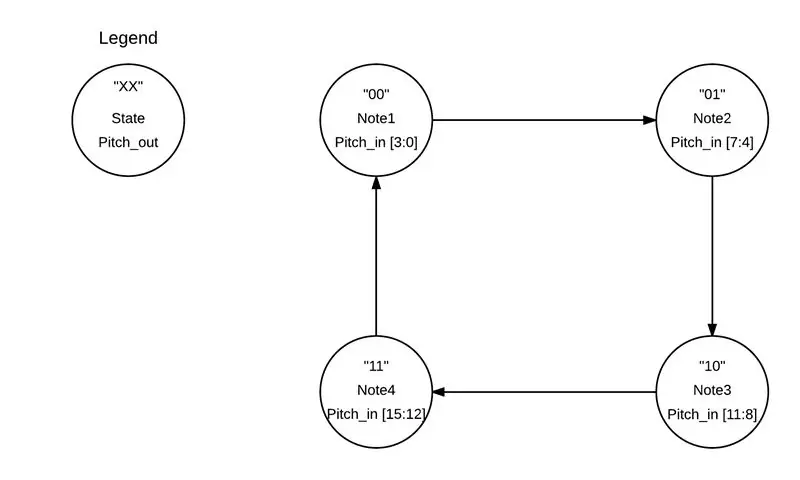

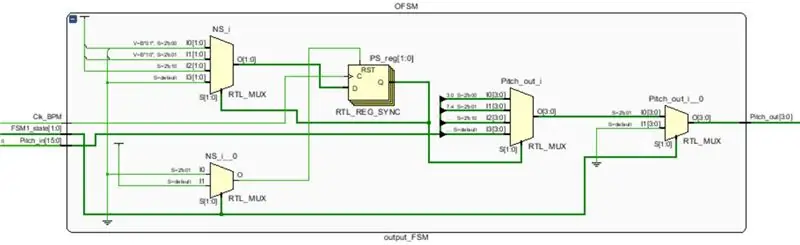

- Schritt 9: Ausgabe FSM

- Schritt 10: Ausgabe FSM

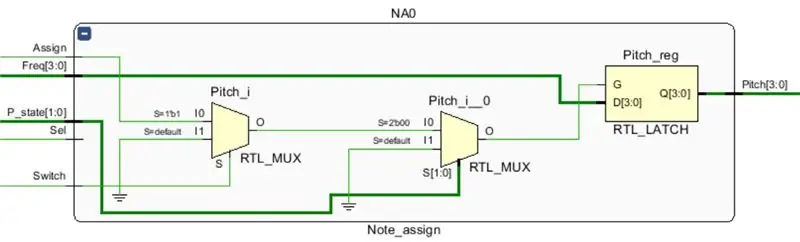

- Schritt 11: Notiz zuweisen

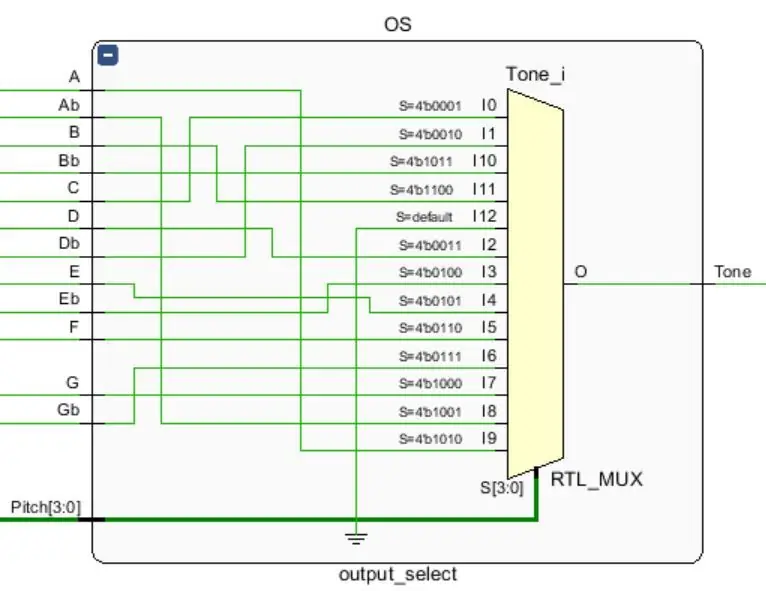

- Schritt 12: Ausgabeauswahl

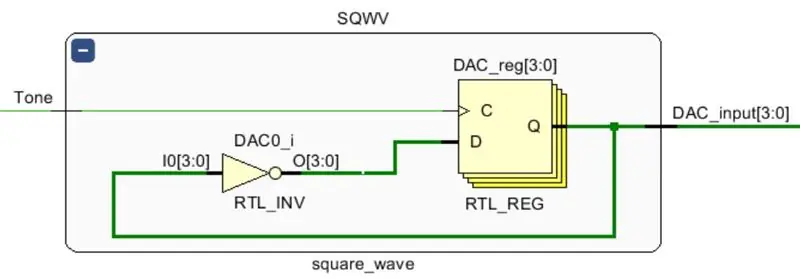

- Schritt 13: Rechteckwelle Gen

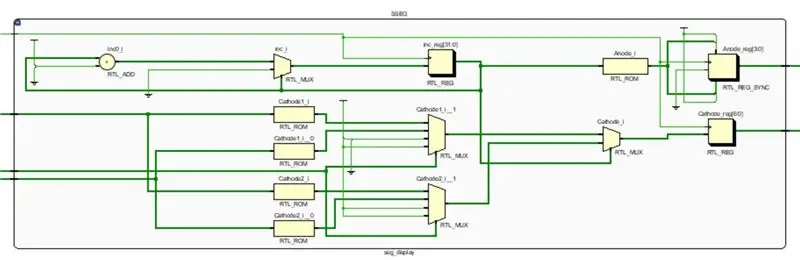

- Schritt 14: 7-Segment-Anzeige

- Schritt 15: Endgültige Auswahl

- Schritt 16: Externe Geräte: DAC

- Schritt 17: Externe Geräte: Lautsprecher

- Schritt 18: Videodemo

- Schritt 19: VHDL-Code

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:21.

- Zuletzt bearbeitet 2025-01-23 12:52.

CPE 133, Cal Poly San Luis Obispo

Projektschöpfer: Jayson Johnston und Bjorn Nelson

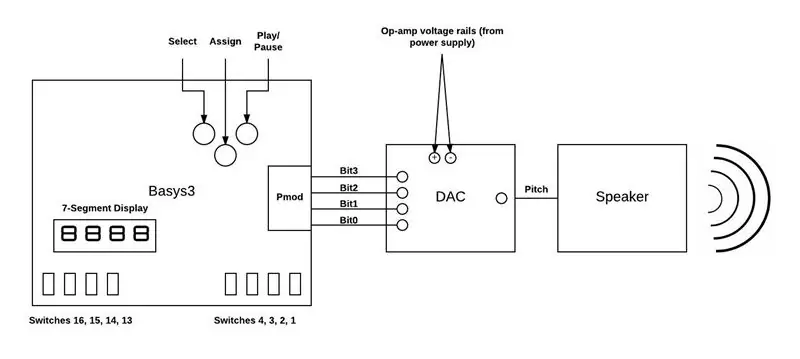

In der heutigen Musikindustrie ist eines der am häufigsten verwendeten „Instrumente“der digitale Synthesizer. Jedes Musikgenre, von Hip-Hop über Pop bis hin zu Country, verwendet einen digitalen Synthesizer im Studio, um die Beats und Sounds zu erzeugen, die sie brauchen, um ihre Musik zum Leben zu erwecken. In diesem Tutorial erstellen wir einen sehr einfachen Synthesizer mit dem Basys 3 FPGA Board.

Der Synthesizer kann vier ausgewählte Viertelnoten mit einer konstanten Anzahl von Schlägen pro Minute spielen. Benutzer verwenden die Schalter, um jede Viertelnote einer musikalischen Tonhöhe zuzuordnen. Für dieses Projekt verwenden wir einen 4-Bit-Digital-Analog-Wandler (DAC), um die Ausgabe von der Platine zu nehmen und in ein analoges Signal umzuwandeln. Der Ausgang des DAC wird dann einem Standard-Computerlautsprecher zugeführt, der unsere Musik erzeugt. Sechzehn diskrete Tonhöhen sind möglich. Wir beschränken unseren Synthesizer auf eine einzelne Oktave von 12 Noten, die zwischen dem mittleren C (261,6 Hz) und B4 (493,9 Hz) liegen. Der Benutzer hat auch die Möglichkeit, mehrere Noten gleichzeitig zuzuweisen, sowie eine Pause durch Drücken von Assign zuzuweisen, während keiner der Tonhöhenschalter nach oben verschoben ist. Wenn jede Note ausgewählt und gespielt wird, wird die Buchstabennote auf der 7-Segment-Anzeige angezeigt. Wir werden auch drei der Tasten auf der Platine verwenden, einen zum Abspielen und Anhalten der Musik, einen zum Zurücksetzen des Synthesizers und Versetzen in den „Auswahlmodus“und den dritten zum Zuweisen einer Tonhöhe für jede Note im Auswahlmodus.

Sobald der Benutzer mit seiner Wahl der Noten zufrieden ist und nach dem Drücken der Play-Taste wird der Synthesizer jede Note nacheinander wiederholt abspielen, bis der Benutzer entweder Pause oder Select drückt.

Hier eine Auflistung der benötigten Geräte:

- Vivado (oder ein beliebiger VHDL-Arbeitsbereich)

- Basys 3 oder ähnliches FPGA-Board

- Digital-Analog-Wandler (mind. 4 Bit)

- Lautsprecher mit Kopfhöreranschluss

- Kabeladern

Schritt 1: Benutzerbedienung des digitalen Sequenzers

Die folgenden Schritte dienen der Bedienung des digitalen Sequenzers. Der digitale Sequenzer unterstützt die Wiedergabe von 12 verschiedenen Tonhöhen (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), die von 261,6 Hz bis 493,9 Hz reichen.

1. Drücken Sie die linke Taste, um das Board in den Auswahlmodus zu versetzen. In diesem Modus werden die 4 Schalter ganz links (Schalter 13 bis 16) zum Speichern eines bestimmten Tonhöhenwerts verwendet.

2. Um eine Auswahl zu treffen, schalten Sie einen der linken Schalter ein und verwenden Sie dann die 4 Schalter ganz rechts (Schalter 1 bis 4), um die gewünschte Tonhöhe auszuwählen. Die einer bestimmten Kombination von rechten Schaltern zugeordnete Tonhöhe wird auf der Sieben-Segment-Anzeige angezeigt, und die Anzeige wird auf die neue zugehörige Tonhöhe aktualisiert, wenn die rechten Schalter auf eine neue Kombination verschoben werden. Sie können eine Pause zuweisen, indem Sie keinem der linken Schalter eine Tonhöhe zuweisen oder der Note eine im Display als 0 angezeigte Tonhöhe zuweisen. Sobald die gewünschte Tonhöhe gefunden wurde und auf dem Display angezeigt wird, drücken Sie die untere Zuweisungstaste, um der Note diese bestimmte Tonhöhe zuzuweisen.

3. Wiederholen Sie Schritt 2 für die drei verbleibenden Noten, indem Sie jeden der verbleibenden linken Schalter einzeln einschalten, die entsprechende Tonhöhe mit den rechten Schaltern wählen und die untere Taste drücken, um der Note die Tonhöhe zuzuweisen. Mehreren Noten kann dieselbe Tonhöhe zugewiesen werden, indem mehr als einer der linken Schalter gleichzeitig nach oben verschoben wird.

4. Nachdem alle Tonhöhen zugewiesen wurden, ist der digitale Sequenzer spielbereit. Um die Noten auf dem Lautsprecher abzuspielen, drücken Sie einfach die rechte Play/Pause-Taste, um mit der Musikwiedergabe zu beginnen. Die Reihenfolge der Wiedergabesequenz spiegelt die den linken Schaltern zugeordneten Tonhöhen von links nach rechts wider. Die Noten werden mit einer festgelegten Anzahl von Schlägen pro Minute in der Reihenfolge 1, 2, 3, 4, 1, 2… gespielt. Das Display zeigt die aktuell gespielte Note an, während die Lautsprecher die Musik abspielen. Um die Musikwiedergabe zu unterbrechen, drücken Sie einfach die rechte Taste, dann stoppt die Musikwiedergabe und ein Pause-Symbol wird auf dem Display angezeigt. Durch erneutes Drücken der rechten Taste wird die Wiedergabe fortgesetzt.

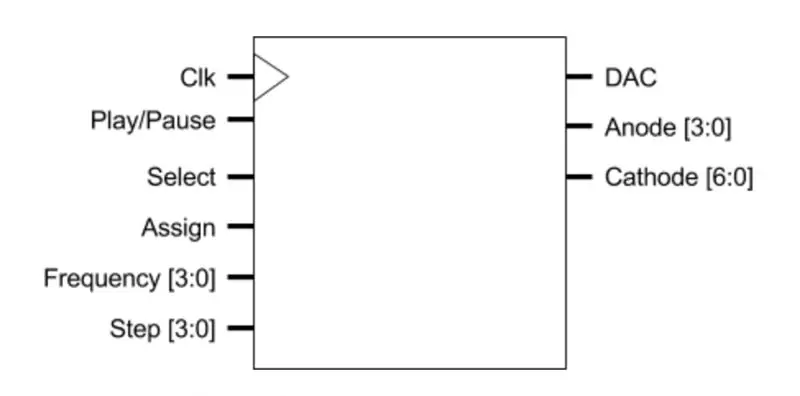

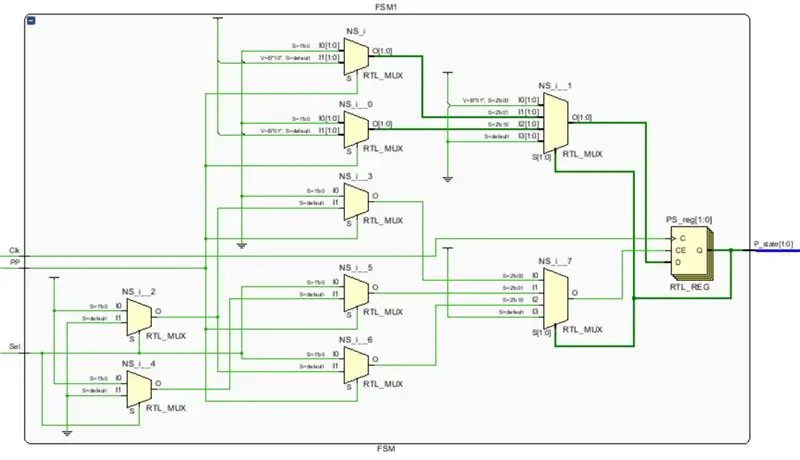

Schritt 2: Technische Details

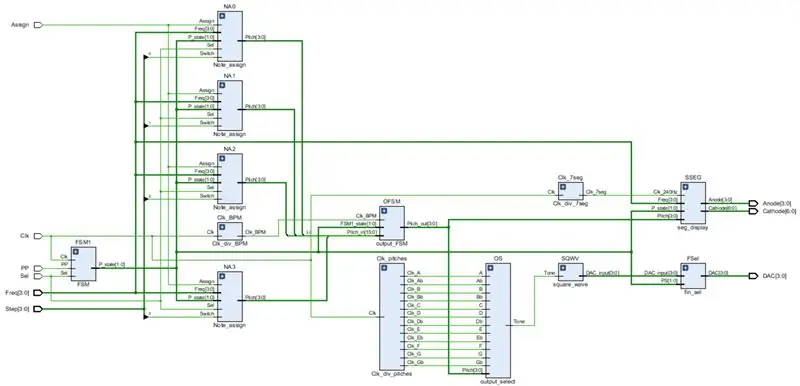

Unser Synthesizer nutzt viele verschiedene digitale Komponenten. Enthalten sind endliche Automaten, Register, Multiplexer, Taktteiler und mehr. Um unseren Synthesizer zu bauen, haben wir 10 einzigartige modulare Dateien verwendet. Anstatt jedes Modul zu einer Komponente zu machen, haben wir die modularen Dateien nach Funktionen unterteilt. Die meisten Module sind daher mehr als eine Komponente. Beachten Sie, dass das obige Bild jeden Block in unserem Top-Design zusammengebunden zeigt.

Wir werden jedes Modul besprechen, indem wir die Ein- und Ausgänge beschreiben, seine Komponenten aufschlüsseln und seinen Zweck im Gesamtdesign erklären. Eine ZIP-Datei ist am Ende der Anleitung enthalten, die jede im Projekt verwendete VHDL-Codedatei enthält.

Eingänge

- Clk (natives Taktsignal)

- PP (Wiedergabe/Pause)

- Sel (Synthesizer in den Auswahlmodus setzen)

- Zuweisen (einer Tonhöhe einen Schritt zuweisen)

- Schritt (die Positionsnotizen)

- Freq (die Schalter, die die gewünschte Tonhöhe erzeugen)

Ausgänge

- Anode (7-Segment-Anoden)

- Kathode (7-Segment-Kathoden)

- DAC (4-Bits, die den DAC ansteuern)

Schritt 3: Technische Details

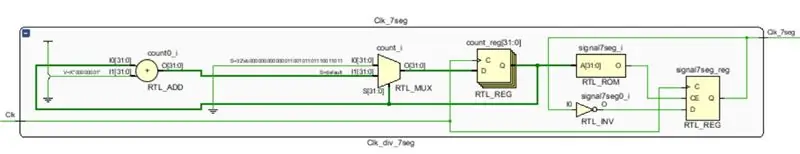

Schritt 4: 7-Segment-Taktteiler

Unser Synthesizer verwendet drei Taktteiler, die alle Signale erzeugen, die in unserem Projekt einem anderen Zweck dienen. Ein Taktteiler nimmt ein natives Taktsignal und erzeugt ein verändertes Signal mit einer Frequenz, die geringer ist als das ursprüngliche Taktsignal. Der native Takt des Basys 3 beträgt 100 MHz. Dies ist die Frequenz, die unsere Taktteiler verwenden. Wenn Sie ein anderes FPGA-Board mit einer anderen nativen Taktfrequenz verwenden, müssen Sie möglicherweise den Code ändern.

Der 7-Segment-Taktteiler erzeugt ein Signal, das die Datei seg_display steuert. Wir werden genauer erklären, wie diese Datei funktioniert, wenn wir zu ihrem Abschnitt kommen. Im Wesentlichen erzeugt dieser Taktteiler ein 240-Hz-Signal, das zum Umschalten zwischen Anoden und Kathoden auf dem Display verwendet wird. Das Signal beträgt 240 Hz, da die Frequenz, bei der das menschliche Auge die Abwesenheit von Licht nicht erkennen kann, bei 60 Hz liegt. Wir verwenden zwei Ziffern. Durch Verdoppeln dieser Frequenz schwingt jede Ziffer mit 60 Hz. Dann verdoppeln wir es, um 240 Hz zu erhalten, weil sich das System nur ändert, wenn das Signal hoch wird, nicht wenn es niedrig wird.

Um dies zu erreichen, nimmt der Teiler das native 100-MHz-Signal und zählt bei jeder steigenden Flanke hoch. Wenn der Zähler 416667 erreicht, geht der Ausgang von niedrig auf hoch oder umgekehrt.

Eingänge

Clk (natives Taktsignal)

Ausgänge

Clk_7seg (zu seg_display)

Komponenten

- D registrieren

- MUX

- Wandler

- Addierer

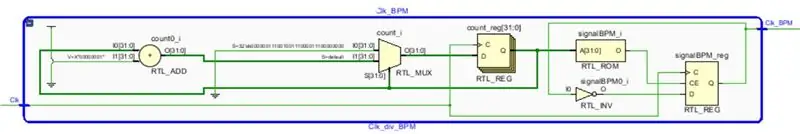

Schritt 5: Beats Per Minute Clock Divider

Der BPM-Taktteiler funktioniert auf ähnliche Weise. Dieser Teiler erzeugt die Taktfrequenz, die das Umschalten zwischen den vier Schritten bei der Ausgabe von Tönen im Spielzustand antreibt. Wir haben uns entschieden, bei 100 BPM zwischen den Noten zu wechseln. Bei 100 BPM wird jede Note 3/5 Sekunden lang gespielt. Das resultierende Signal hätte eine Frequenz von 1,67 Hz.

Um ein Signal dieser Frequenz zu erzeugen, verwendeten wir wieder ein Zählsystem, aber diesmal waren es 60 Millionen. Jedes Mal, wenn der Zähler 60 Millionen erreichte, wechselte das Ausgangssignal hoch oder niedrig.

Eingänge

Clk (native Taktfrequenz)

Ausgänge

Clk_BPM (an Ausgabe_FSM)

Komponenten

- D registrieren

- MUX

- Wandler

- Addierer

Schritt 6: Tonhöhentaktteiler

Der Pitches Clock Divider ist der größte unserer Clock-Teiler. Dieser Teiler gibt 12 verschiedene Signale aus, die den 12 verschiedenen Noten entsprechen, die unser Synthesizer spielen kann. Aus musiktheoretischen Grundkenntnissen haben wir abgeleitet, dass ein Bit oder ein Bus mit einer Frequenz schwingen kann, die der Frequenz von Musiknoten entspricht. Um zu sehen, welche Frequenzen wir verwendet haben, schauen Sie hier. Wir haben die vierte Oktave der Tonhöhen verwendet.

Hier wird das gleiche Zählsystem verwendet. Die spezifischen Werte, auf die wir gezählt haben, finden Sie in der Datei mit der Bezeichnung Clk_div_pitches.

Eingänge

Clk (native Taktfrequenz)

Ausgänge

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (zu output_select)

Komponenten

- D registrieren

- MUX

- Wandler

- Addierer

Schritt 7: Play/Pause/Select State Machine

In unserem Projekt gibt es zwei Finite State Machines (FSM). Ein FSM ist ein logisches Gerät, das aus einer endlichen Anzahl von Zuständen nur in einem Zustand existieren kann. Unter Verwendung eines FSM kann eine digitale Schaltung basierend auf einer Kombination von Eingängen in einen neuen Zustand übergehen. Unter Verwendung der Eingangslogik ändert sich der Zustand eines FSM, wenn eine steigende Taktflanke auftritt. Aus dem Zustand und den Eingängen in die Schaltung können Sie eine Ausgangslogik erstellen, die Ausgänge liefert, die nur existieren, wenn sich der FSM in einem bestimmten Zustand befindet.

Die PPS-Zustandsmaschine ist die erste FSM in unserer Schaltung. Es gibt drei Zustände in diesem FSM; Wiedergabe-, Pause- und Auswahlmodus. Um sich durch die verschiedenen Zustände zu bewegen, haben wir die Schaltflächen PP und Auswahl verwendet. Sehen Sie sich das obige Zustandsdiagramm an, um zu sehen, wie Übergänge zwischen Zuständen auftreten. Wir haben diesen FSM-Übergang an der steigenden Flanke des nativen 100-MHz-Takts vorgenommen, so dass es unmöglich ist, dass das Gerät selbst für eine sehr kurze Zeit nicht übergeht, wenn eine der Tasten gedrückt wird. Der aktuelle Zustand (P_state) ist die einzige Ausgabe dieses Moduls.

Eingänge

- Clk (native Taktfrequenz)

- Sel (linke Taste)

- PP (rechte Taste)

Ausgänge

P_state (aktueller Zustand, an output_FSM, note_assign, seg_dsiplay, final_select)

Komponenten

- MUX

- D registrieren

Schritt 8: Play/Pause/Select State Machine

Schritt 9: Ausgabe FSM

Dies ist die zweite FSM, auf die im vorherigen Abschnitt verwiesen wurde. Dieser FSM hat eine andere Funktion als der andere, aber die Grundlage für diesen ist im Wesentlichen die gleiche.

Die Ausgabe-FSM arbeitet nur, wenn der gegenwärtige Zustand von der ersten FSM "01" (der Wiedergabezustand) ist. Im Wesentlichen ist dies die Freigabe für das Modul. Wenn der Zustand "01" ist, wird die FSM zwischen den Zuständen an der ansteigenden Flanke des BPM-Taktsignals umschalten. Wir tun dies, weil der output_FSM steuert, welche Binärzahl für die ausgewählte Tonhöhe an die Module output_select und seg_display gesendet wird. Der FSM hat einen 16-Bit-Eingang, der vom Note-Assign-Modul kommt, das als nächstes behandelt wird. Im Zustand „00“für den Ausgang_FSM gibt das Modul „xxxx“für die erste zugewiesene Note aus. Dann wird in "01" "yyyy" für die zweite Note ausgegeben usw. für jede Note, bevor zur ersten Note zurückgerollt wird. Siehe das Zustandsdiagramm oben.

Diese FSM unterscheidet sich von der ersten, da es keine Eingangslogik gibt, um das Umschalten zwischen den Zuständen zu steuern. Stattdessen wird die FSM nur arbeiten, wenn der Zustand von der ersten FSM "01" ist, und dann wechselt diese FSM zwischen den Zuständen nur bei der steigenden Flanke des Taktsignals. Ein weiterer Unterschied besteht darin, dass dieses Modul über eine Ausgangslogik verfügt, dh es gibt nicht den aktuellen Zustand aus, sondern die Binärzahl für die Tonhöhe in diesem Zustand.

Eingänge

- Clk_BPM (BPM-Taktsignal vom Taktteiler)

- FSM1_state (PS von PPS FSM)

- Pitch_in (Pitches von note_assign)

Ausgänge

Pitch_out (eine Tonhöhe nach der anderen, zu output_select und seg_display)

Komponenten

- MUX

- D registrieren

Schritt 10: Ausgabe FSM

Schritt 11: Notiz zuweisen

Das Notenzuweisungsmodul ist dafür verantwortlich, der Positionsnote oder dem Schritt tatsächlich eine Tonhöhe zuzuweisen. Dieses Modul ist eigentlich ganz einfach. Es prüft zunächst, ob sich die Schaltung im Zustand "Auswahl" befindet und ob ein Stufenschalter (ganz links) hoch ist. Wenn dies wahr ist und die Zuweisungstaste gedrückt wird, entspricht der Ausgang des Moduls der binären Zahl, die durch die Frequenzschalter (ganz rechts) dargestellt wird.

Ursprünglich hatten wir versucht, ein Modul zu entwickeln, das tatsächlich eines der Pitch-Clock-Signale am Ausgang speichert, aber wir hatten Probleme damit, dass sich der Ausgang änderte, um den Eingangstaktsignalen zu folgen. Dies ist das einzige Modul, das im endgültigen Design mehr als einmal verwendet wird. Jedem Step ist ein note_assign-Modul zugeordnet, und deshalb erhält jede Instanz des Moduls ein Bit des Step-Busses.

Eingänge

- P_state (aktueller Zustand von PPS FSM)

- Sel (linke Taste)

- Schalter (einstufiger Schalter)

- Freq (ganz rechts Schalter für Tonhöhe)

- Zuweisen (untere Taste, weist eine Note zu)

Ausgänge

Tonhöhe (Binärzahl, zum Ausgang_FSM)

Komponenten

- MUX

- D registrieren

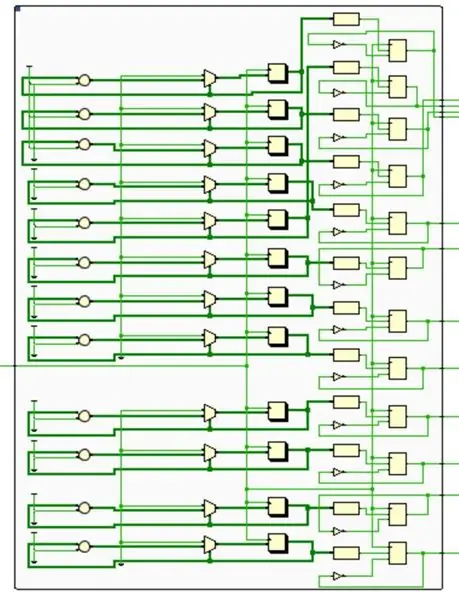

Schritt 12: Ausgabeauswahl

Output Select ist dafür verantwortlich, die Binärzahl für eine Tonhöhe zu nehmen und diese mit ihrem entsprechenden Taktsignal zu verbinden. Trotz seiner Größe ist dies auch ein relativ einfaches Modul. Output_select ist im Wesentlichen ein binärer Decoder, der die binäre Zahl für eine Tonhöhe zu einem bestimmten Taktsignal decodiert. Tatsächlich funktionierte hier die Zuordnung des Ausgangs zu einer Taktfrequenz besser als beim Modul note_assign, da dieses Modul lediglich die Taktsignale mit der Binärzahl, die den Steuereingang repräsentiert, MUX-MUX war.

Wir entschuldigen uns für das seltsame Routing, Vivado hat die Tonhöhensignale alphabetisch für die Datei clk_div_pitches organisiert, aber für diese Datei hat es sie nach aufsteigenden Binärzahlen organisiert, wodurch die Tonhöhen in einer anderen Reihenfolge angeordnet sind. Beachten Sie auch, dass, wenn die Binärzahl von output_FSM "0000" oder etwas größer als "1100" war, der MUX durch ein flaches '0'-Signal gesendet wird.

Eingang

- Tonhöhe (von output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (Pitch-Clock-Signale)

Ausgabe

Tone (ein einzelnes Bit, das dem ausgewählten Taktsignal entspricht, zu square_wave)

Komponenten

MUX

Schritt 13: Rechteckwelle Gen

Das Modul square_wave ist der Generator für die Rechteckwelle, die von der Platine an den DAC ausgegeben wird. Unter Verwendung des Tonsignals aus der vorherigen Datei invertiert diese Rechteckwelle die 4-Bit-Zahl zwischen "0000" und "1111" an der steigenden Flanke von Tone. Tone ist eine bestimmte Tonhöhenfrequenz, daher erzeugt square_wave eine Welle mit einer anderen Frequenz, wenn output_FSM in einen anderen Zustand übergeht. Die 4-Bit-Ausgabe dieses Moduls geht an das Modul fin_sel, wo die Logik vorschreibt, ob dieser Bus basierend auf dem Zustand von PPS FSM ausgegeben wird.

Eine Alternative zu diesem Rechteckwellengenerator ist die Erzeugung einer Sinuswelle. Während dies höchstwahrscheinlich einen besseren Endton erzeugen würde, ist es erheblich schwieriger zu implementieren, daher haben wir uns dafür entschieden, nur eine Rechteckwelle zu erzeugen.

Eingänge

Ton (oszillierendes Bit von output_select)

Ausgänge

DAC_input (oszillierender 4-Bit-Bus, der sich mit der gleichen Tonfrequenz ändert)

Komponenten

- Wandler

- D registrieren

Schritt 14: 7-Segment-Anzeige

Das Modul seg_display steuert die 7-Segment-Anzeige auf unserem basys Board. Innerhalb des Moduls laufen zwei Prozesse ab. Der erste Prozess decodiert Freq im "Auswahl"-Zustand oder Pitch im "Play"-Modus. Im "Pause"-Modus dekodiert das Modul, um das Pause-Symbol anzuzeigen. Wenn Sie sich den VHDL-Code ansehen, können Sie sehen, dass der Binärdecoder die Eingabe tatsächlich in zwei verschiedene Signale decodiert, Kathode1 und Kathode2. Kathode1 repräsentiert den Buchstaben, der der anzuzeigenden Tonhöhe entspricht, und Kathode2 repräsentiert das flache Symbol (b), falls es eines gibt. Der Grund dafür hängt mit dem zweiten Prozess zusammen, der vom Modul seg_display durchgeführt wird.

Auf einem basys3-Board hat die Segmentanzeige gemeinsame Kathoden. Während die Anoden steuern, welche Ziffer eingeschaltet ist, steuern die Kathoden, welche Segmente eingeschaltet sind. Da das Display über gemeinsame Kathoden verfügt, können Sie nur einen Satz von Segmenten gleichzeitig anzeigen. Das stellt für dieses Projekt ein Problem dar, da wir einen Buchstaben an der ersten Ziffer und ggf. gleichzeitig das flache Symbol anzeigen wollen. Erinnern Sie sich jetzt an das 7seg-Taktsignal? Um dieses Problem zu umgehen, wechseln wir die Anoden und Kathoden beim 7seg-Taktsignal hin und her. Da das Taktsignal 240 Hz beträgt und wir zwei Ziffern verwenden, schwingt jede Ziffer mit 60 Hz. Für das menschliche Auge sieht es so aus, als ob die Ziffern überhaupt nicht oszillieren.

Beachten Sie auch, dass das basys3-Board-Display eine negative Logik verwendet. Das bedeutet, wenn eine Anode oder Kathode auf '0' gesetzt ist, ist diese Ziffer oder dieses Segment eingeschaltet und umgekehrt.

Eingänge

- Tonhöhe (Binärzahl für eine Note, im Spielzustand verwendet)

- Freq (Frequenzschalter, verwendet im Auswahlzustand)

- P_state (aktueller Zustand von PPS FSM)

- Clk_240Hz (Taktsignal von Clk_div_7seg, doppelt 120, da wir nur die steigende Flanke verwenden)

Ausgänge

- Kathode (Bus, der Segmente auf dem Display steuert, Endausgang)

- Anode (Bus, der die Ziffern auf dem Display steuert, Endausgang)

Komponenten

- Verriegeln

- MUX

- D registrieren

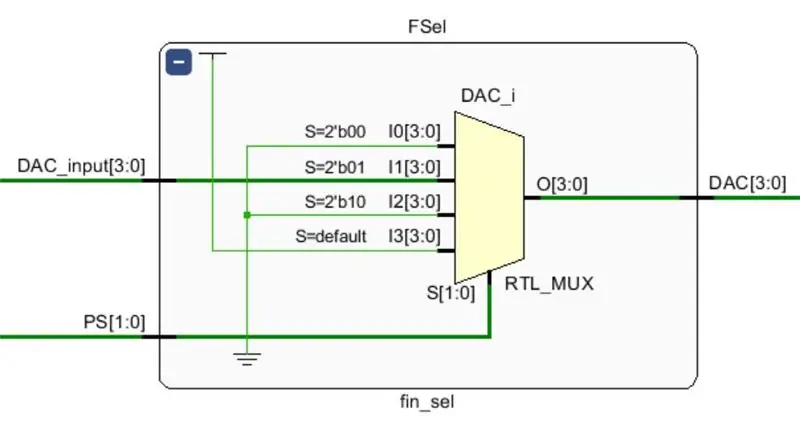

Schritt 15: Endgültige Auswahl

Final select ist das letzte Modul, das in diesem Projekt verwendet wird. Ein weiteres einfaches Modul, dieses Modul steuert den endgültigen Ausgang, der an den DAC geht. Im Zustand "Auswahl" oder "Pause" gibt das Modul ein statisches "0000" aus, damit keine Musik aus den Lautsprechern abgespielt wird. Im "Play"-Zustand gibt das Modul die oszillierenden 4 Bits aus, wie durch square_wave bestimmt.

Eingänge

- P_state (aktueller Zustand von PPS FSM)

- DAC_input (die oszillierenden 4 Bits von square_wave)

Ausgänge

DAC (entspricht DAC_input im Wiedergabezustand, endgültige Ausgabe)

Komponenten

MUX

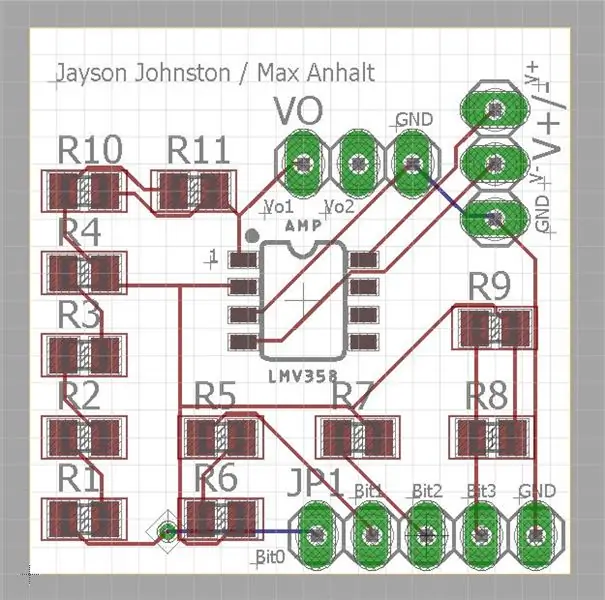

Schritt 16: Externe Geräte: DAC

Ein Digital-Analog-Wandler (DAC) nimmt ein diskretes Signal und wandelt es in ein kontinuierliches Signal um. Unser DAC hat vier Bits und besteht aus einem Summierverstärker. Durch die Verwendung eines Widerstandsverhältnisses in der Versorgungs- und Rückkopplungsschleife konnten wir ein System erstellen, das auf 16 verschiedenen Pegeln ausgibt, die durch das "Summieren" jedes Zweigs erzeugt werden. Bit0, der oberste Zweig, hat das geringste Gewicht und trägt aufgrund des höheren Widerstands der Zweige das kleinste Potenzial bei, wenn er hoch ist. Das Gewicht nimmt zu, wenn Sie die Äste hinuntergehen. Wenn Sie mit den Bit-Eingängen binär aufwärts und dann rückwärts zählen würden, würden die Ausgangsspannungen wie eine schrittweise Sinuswelle aussehen. Der Eingang zum DAC wurde mit einem der PMODs auf der Platine verbunden, um das 4-Bit-Signal zu übertragen.

Der DAC wurde ursprünglich für einen Elektrotechnik-Kurs zusammengebaut und von uns entworfen und gelötet, nicht im Laden gekauft. Oben ist ein Bild der Designdatei zum Erstellen der Leiterplatte.

Schritt 17: Externe Geräte: Lautsprecher

Für dieses Projekt werden Sie keine super schönen Lautsprecher kaufen wollen. Wie Sie sehen können, ist der Sound ziemlich einfach. Wir gingen und kauften einen 8-Dollar-Satz Computerlautsprecher von Best Buy. Alles mit Kopfhöreranschluss funktioniert einwandfrei. Monoton funktioniert auch gut. Sie können sogar Kopfhörer verwenden, aber Sie könnten sie ausblasen!

Um den Ausgang des DAC mit den Lautsprechern zu verbinden, haben wir Überbrückungskabel verwendet und dann das Ausgangskabel an die Spitze der Kopfhörerbuchse und das Kabel für die Masse an die Basis gehalten. Wir haben versucht, die Kabel mit Isolierband zu befestigen, aber es verursachte viele Störungen. Das Ausprobieren eines anderen Bandstils könnte dieses Problem lösen.

Bei unseren Lautsprechern haben wir sie auf die höchste Stufe gestellt und ein ordentlich lautes Geräusch bekommen.

Und das ist der letzte Schritt, um aus einem FPGA-Board einen digitalen Sequenzer zu erstellen! Gehen Sie zu den nächsten beiden Abschnitten, um unseren gesamten VHDL-Code herunterzuladen und den Sequenzer in Aktion zu sehen.

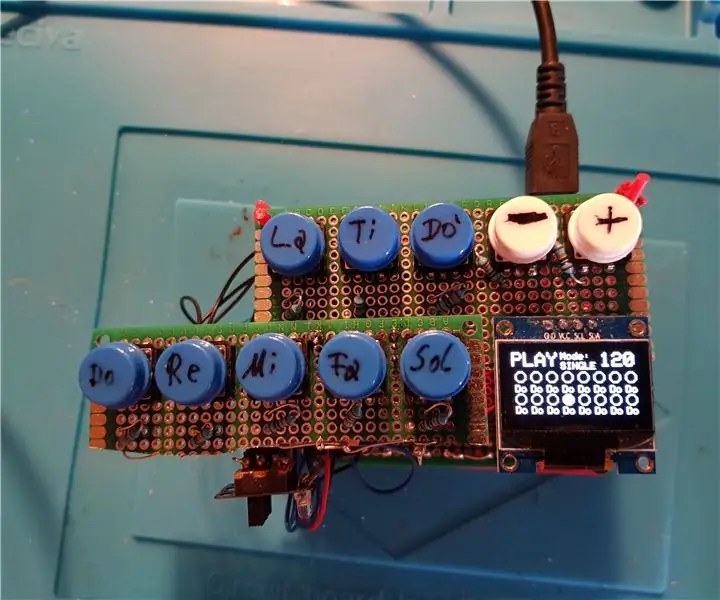

Schritt 18: Videodemo

Dieses Video zeigt die endgültige Version des Arbeitsprojekts, einschließlich der Zuordnung der Schalter zu 4 verschiedenen Tonhöhen und der Lautsprecher, die die entsprechenden Noten spielen.

Schritt 19: VHDL-Code

Hier ist der Code für das gesamte Projekt, einschließlich der Constraint- und Sim-Dateien, die beim Erstellen des Sequenzers verwendet wurden. Beachten Sie, dass nicht verwendete Designdateien dies in der Architektur angeben.

Empfohlen:

Erste Schritte mit Python: 7 Schritte (mit Bildern)

Erste Schritte mit Python: Programmieren ist großartig! Es ist kreativ, macht Spaß und gibt Ihrem Gehirn ein mentales Training. Viele von uns wollen etwas über Programmieren lernen, aber überzeugen sich selbst davon, dass wir es nicht können. Vielleicht hat es zu viel Mathematik, vielleicht der Jargon, der erschreckend herumgeworfen wird

DoReMiQuencer - Programmierbarer MIDI-Sequenzer mit Tastatur - Gunook

DoReMiQuencer - Programmable MIDI Sequencer With Keyboard: Dieses Gerät wurde für die Verwendung mit VCVRack entwickelt, einem von VCV erstellten virtuellen modularen Synthesizer, kann aber als universeller MIDI-Controller dienen. Es dient je nach ausgewähltem Modus als MIDI-Sequenzer oder Tastatur. Die dem ke zugeordneten MIDI-Noten

Heritage - Keramik im Kontext digitaler und analoger Techniken 2015 – 3 Schritte (mit Bildern)

Heritage - Keramik im Kontext digitaler und analoger Techniken 2015: Keramik war bisher ein Handwerk mit geringem digitalen Einfluss. Aus diesem Grund war es spannend, dieses Handwerk mit einer neuen Technologie zu verbinden. Ausgangspunkt war eine uralte Form und ein CNC Styropor.DESIGNBOOM

Programmierbarer RGB-LED-Sequenzer (mit Arduino und Adafruit Trellis) - Gunook

Programmierbarer RGB-LED-Sequenzer (mit Arduino und Adafruit Trellis): Meine Söhne wollten farbige LED-Streifen, um ihre Schreibtische zu beleuchten, und ich wollte keinen RGB-Streifen-Controller aus der Dose verwenden, weil ich wusste, dass sie sich mit den festen Mustern langweilen würden diese Controller haben. Ich dachte auch, es wäre eine großartige Gelegenheit

Digitaler 3D-Bildbetrachter - "Das DigiStereopticon": 6 Schritte (mit Bildern)

Digitaler 3D-Bildbetrachter - "Das DigiStereopticon": Stereoskopische Fotografie ist in Ungnade gefallen. Das liegt wahrscheinlich daran, dass man nicht gerne eine spezielle Brille tragen muss, um Familienschnappschüsse zu sehen. Hier ist ein lustiges kleines Projekt, das Sie in weniger als einem Tag erstellen können, um Ihr 3D-Bild zu erstellen