Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:18.

- Zuletzt bearbeitet 2025-01-23 12:52.

Ich werde analysieren, wie die Herausforderung des Netzteildesigns von DC-DC Technologies bewältigt wird.

Die Entwickler von Stromversorgungssystemen sehen sich einem ständigen Druck des Marktes ausgesetzt, Wege zu finden, um das Beste aus der verfügbaren Energie herauszuholen. Bei tragbaren Geräten verlängert eine höhere Effizienz die Batterielebensdauer und bringt mehr Funktionalität in kleinere Pakete. In Servern und Basisstationen können durch Effizienzsteigerungen direkt Infrastruktur (Kühlsysteme) und Betriebskosten (Stromrechnungen) eingespart werden. Um den Marktanforderungen gerecht zu werden, verbessern Systemdesigner die Leistungsumwandlungsprozesse in mehreren Bereichen, darunter effizientere Schalttopologien, Gehäuseinnovationen und neue Halbleiterbauelemente auf Basis von Siliziumkarbid (SiC) und Galliumnitrid (GaN).

Schritt 1: Verbesserung der Schaltwandlertopologie

Um die verfügbare Leistung voll auszuschöpfen, verwenden die Menschen zunehmend Designs, die auf Schalttechnologie statt auf Lineartechnologie basieren. Das Schaltnetzteil (SMPS) hat eine Wirkleistung von über 90%. Dies verlängert die Batterielebensdauer tragbarer Systeme, senkt die Stromkosten für große Geräte und spart Platz, der bisher für Kühlkörperkomponenten verwendet wurde.

Der Wechsel zu einer geschalteten Topologie hat bestimmte Nachteile, und das komplexere Design erfordert von Designern mehrere Fähigkeiten. Konstrukteure müssen mit analogen und digitalen Technologien, Elektromagnetik und Regelungstechnik vertraut sein. Entwickler von Leiterplatten (PCBs) müssen elektromagnetischen Störungen (EMI) mehr Aufmerksamkeit schenken, da hochfrequente Schaltwellenformen Probleme in empfindlichen analogen und HF-Schaltungen verursachen können.

Vor der Erfindung des Transistors wurde das Grundkonzept der Schaltstromumwandlung vorgeschlagen: zum Beispiel das 1910 erfundene induktive Entladungssystem vom Kate-Typ, das einen mechanischen Vibrator verwendet, um einen Flyback-Aufwärtswandler für ein Automobilzündsystem zu implementieren.

Die meisten Standardtopologien gibt es seit Jahrzehnten, aber das bedeutet nicht, dass Ingenieure Standarddesigns nicht an neue Anwendungen anpassen, insbesondere Regelkreise. Die Standardarchitektur verwendet eine feste Frequenz, um eine konstante Ausgangsspannung aufrechtzuerhalten, indem ein Teil der Ausgangsspannung rückgekoppelt (Spannungsmodussteuerung) oder der induzierte Strom (Strommodussteuerung) unter verschiedenen Lastbedingungen gesteuert wird. Designer verbessern sich ständig, um die Mängel des grundlegenden Designs zu überwinden.

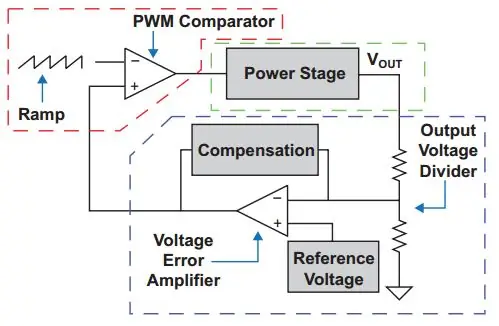

Fig. 1 ist ein Blockschaltbild eines grundlegenden Spannungsmodussteuerungs-(VMC-)Systems mit geschlossenem Regelkreis. Die Endstufe besteht aus einem Leistungsschalter und einem Ausgangsfilter. Der Kompensationsblock umfasst einen Ausgangsspannungsteiler, einen Fehlerverstärker, eine Referenzspannung und eine Schleifenkompensationskomponente. Ein Pulsbreitenmodulator (PWM) verwendet einen Komparator, um das Fehlersignal mit einem festen Rampensignal zu vergleichen, um eine Ausgangsimpulsfolge zu erzeugen, die proportional zum Fehlersignal ist.

Obwohl die verschiedenen Lasten des VMC-Systems strenge Ausgaberegeln haben und leicht mit dem externen Takt synchronisiert werden können, hat die Standardarchitektur einige Nachteile. Die Schleifenkompensation reduziert die Bandbreite des Regelkreises und verlangsamt das Einschwingverhalten; der Fehlerverstärker erhöht den Betriebsstrom und reduziert die Effizienz.

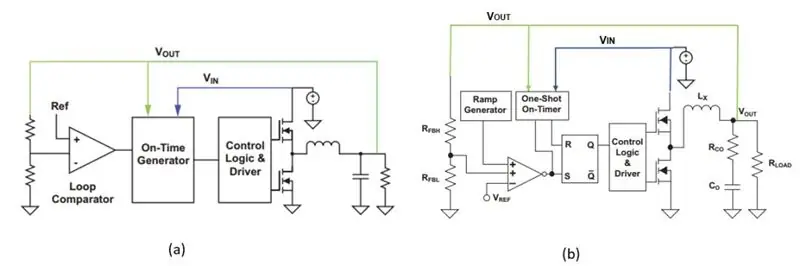

Das Steuerschema der konstanten Einschaltzeit (COT) bietet eine gute Übergangsleistung ohne Schleifenkompensation. Die COT-Steuerung verwendet einen Komparator, um die geregelte Ausgangsspannung mit der Referenzspannung zu vergleichen: Wenn die Ausgangsspannung kleiner als die Referenzspannung ist, wird ein Impuls mit fester Einschaltzeit erzeugt. Bei niedrigen Tastverhältnissen führt dies zu einer sehr hohen Schaltfrequenz, sodass der adaptive COT-Regler eine mit den Eingangs- und Ausgangsspannungen variierende Einschaltzeit erzeugt, die die Frequenz im stationären Zustand nahezu konstant hält. Die D-CAP-Topologie von Texas Instrument ist eine Verbesserung gegenüber dem adaptiven COT-Ansatz: Der D-CAP-Controller fügt dem Feedback-Komparatoreingang eine Rampenspannung hinzu, die die Jitter-Leistung verbessert, indem das Rauschband in der Anwendung reduziert wird. Abbildung 2 ist ein Vergleich der COT- und D-CAP-Systeme.

Abbildung 2: Vergleich der Standard-COT-Topologie (a) und der D-CAP-Topologie (b) (Quelle: Texas Instruments) Es gibt verschiedene Varianten der D-CAP-Topologie für unterschiedliche Anforderungen. Der Halbbrücken-PWM-Controller TPS53632 verwendet beispielsweise die D-CAP+-Architektur, die hauptsächlich in Hochstromanwendungen verwendet wird und Leistungspegel von bis zu 1 MHz in 48-V-zu-1-V-POL-Wandlern mit Wirkungsgraden von bis zu 92 % steuern kann.

Im Gegensatz zu D-CAP fügt die D-CAP+-Rückkopplungsschleife eine Komponente hinzu, die proportional zum induzierten Strom ist, um eine präzise Statiksteuerung zu ermöglichen. Der Verstärker mit erhöhtem Fehler verbessert die Genauigkeit der DC-Last unter einer Vielzahl von Netz- und Lastbedingungen.

Die Ausgangsspannung des Controllers wird vom internen DAC eingestellt. Dieser Zyklus beginnt, wenn die Stromrückführung den Fehlerspannungspegel erreicht. Diese Fehlerspannung entspricht der verstärkten Spannungsdifferenz zwischen der DAC-Sollwertspannung und der Rückkopplungsausgangsspannung.

Schritt 2: Verbessern Sie die Leistung unter leichten Lastbedingungen

Bei tragbaren und tragbaren Geräten besteht die Notwendigkeit, die Leistung unter leichten Lastbedingungen zu verbessern, um die Batterielebensdauer zu verlängern. Viele tragbare und tragbare Anwendungen befinden sich die meiste Zeit in einem "temporären Schlaf"- oder "Schlaf"-Standby-Modus mit geringem Stromverbrauch, der nur als Reaktion auf Benutzereingaben oder periodische Messungen aktiviert wird, sodass der Stromverbrauch im Standby-Modus minimiert wird. Es hat oberste Priorität.

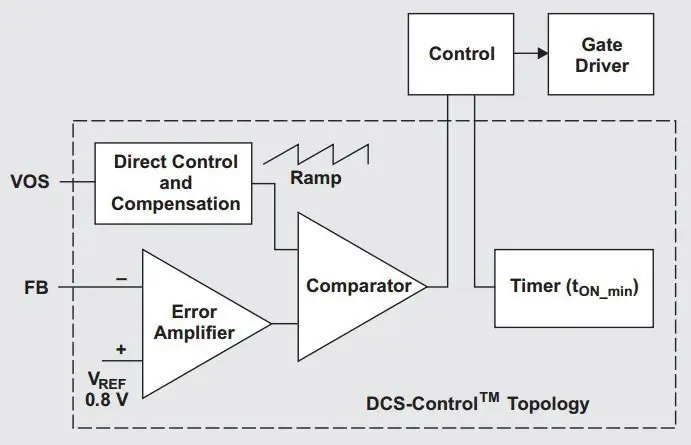

Die DCS-ControlTM-Topologie (Direct Control to Seamless Transition to Energy Saver Mode) kombiniert die Vorteile von drei verschiedenen Steuerschemata (dh Hysteresemodus, Spannungsmodus und Strommodus), um die Leistung unter leichten Lastbedingungen zu verbessern, insbesondere beim Übergang in oder wenn Verlassen des Leichtlastzustandes. Diese Topologie unterstützt PWM-Modi für mittlere und schwere Lasten sowie den Energiesparmodus (PSM) für leichte Lasten.

Während des PWM-Betriebs arbeitet das System mit seiner Nennschaltfrequenz basierend auf der Eingangsspannung und steuert die Frequenzänderung. Wenn der Laststrom abnimmt, schaltet der Umrichter auf das PSM um, um den hohen Wirkungsgrad aufrechtzuerhalten, bis er auf eine sehr geringe Last abfällt. Bei PSM nimmt die Schaltfrequenz linear mit dem Laststrom ab. Beide Modi werden von einem einzigen Steuerblock gesteuert, sodass der Übergang von PWM zu PSM nahtlos ist und die Ausgangsspannung nicht beeinflusst.

Abbildung 3 ist ein Blockschaltbild des DCS-ControlTM. Der Regelkreis nimmt Informationen über die Änderung der Ausgangsspannung auf und führt sie direkt an den schnellen Komparator zurück. Der Komparator stellt die Schaltfrequenz (als Konstante für stationäre Betriebsbedingungen) ein und reagiert sofort auf dynamische Laständerungen. Die Spannungsrückkopplungsschleife regelt die DC-Last genau. Das intern kompensierte Regelnetzwerk ermöglicht einen schnellen und stabilen Betrieb mit kleinen externen Komponenten und Kondensatoren mit niedrigem ESR.

Abbildung 3: Implementierung der DCS-ControlTM-Topologie im Abwärtswandler TPS62130 (Quelle: Texas Instruments)

Der synchrone Schaltnetzteil TPS6213xA-Q1 basiert auf der DCS-ControlTM-Topologie und ist für POL-Anwendungen mit hoher Leistungsdichte optimiert. Die typische Schaltfrequenz von 2,5 MHz ermöglicht die Verwendung kleiner Induktivitäten und bietet ein schnelles Einschwingverhalten und eine hohe Genauigkeit der Ausgangsspannung. Der TPS6213 arbeitet in einem Eingangsspannungsbereich von 3 V bis 17 V und kann bis zu 3 A Dauerstrom zwischen 0,9 V und 6 V Ausgangsspannung liefern.

Empfohlen:

Wie man eine Babygewichtsmaschine mit Arduino Nano, HX-711 Wägezelle und OLED 128X64 herstellt -- Kalibrierung des HX-711: 5 Schritte

Wie man eine Babygewichtsmaschine mit Arduino Nano, HX-711-Wägezelle und OLED 128X64 herstellt || Kalibrierung von HX-711: Hallo Instructables, vor wenigen Tagen wurde ich Vater eines süßen Babys?. Als ich im Krankenhaus war, stellte ich fest, dass das Gewicht des Babys so wichtig ist, um das Wachstum des Babys zu überwachen. Also ich habe eine Idee? um eine Babygewichtsmaschine von meinem Selbst zu machen. In diesem Instructable ich

Gewusst wie: Geschwindigkeit des Motors steuern?: 5 Schritte (mit Bildern)

Gewusst wie: Geschwindigkeit des Motors steuern?: Wenn Sie ein paar DC-Motoren herumliegen haben, kommt Ihnen die erste Frage in den Sinn, wie ich die Geschwindigkeit dieser Motoren kontrolliere! Also in diesem Instructables werde ich zeigen, wie einfach es ist! Sie fühlen sich faul, Sie können Videos auf meinem Kanal ansehen Auch Huge Tha

Gewusst wie: Platzieren von Bandspielern auf Ihrem Myspace – wikiHow

Gewusst wie: Setzen von Band-Playern auf Ihr Myspace: In diesem anweisbaren werde ich Ihnen beibringen, wie Sie die Musik-Player von Myspace Band auf Ihr Myspace-Profil setzen. Hinweis: Dies ist mein erstes instructable

Wie man Firefox zum nützlichsten Webbrowser macht, den es gibt: 8 Schritte

Wie man Firefox zum nützlichsten Webbrowser macht, den es gibt: Wenn Sie noch nicht davon überzeugt sind, dass Firefox besser ist als alles da draußen, finden Sie hier ein paar Tipps und Optimierungen, die Sie zum Umsteigen bringen werden. Wenn Sie Firefox verwenden, wussten Sie vielleicht noch nichts davon

Eine Apfelgirlande für den Herbst oder den Schulanfang herstellen – wikiHow

Wie man eine Apfelgirlande für den Herbst oder den Schulanfang herstellt: Anjeanette von RootsAndWingsCo hat diese entzückende Apfelgirlande aus Filz und Material hergestellt. Es war ein einfaches Projekt, das selbst diejenigen, die sagen, dass sie nicht nähen können, tun können! (Solange Sie Ihre Nadel einfädeln können.)