Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:18.

- Zuletzt bearbeitet 2025-01-23 12:52.

Ich schreibe dieses instructable, weil ich es ein wenig schwierig fand, einen Referenz-VHDL-Code zu bekommen, um zu lernen und einen Cache-Controller zu entwerfen. Also habe ich selbst einen Cache-Controller von Grund auf neu entworfen und erfolgreich auf FPGA getestet. Ich habe hier einen einfachen direkt zugeordneten Cache-Controller vorgestellt sowie ein ganzes Prozessor-Speicher-System modelliert, um den Cache-Controller zu testen. Ich hoffe, Sie finden dieses instructable nützlich als Referenz, um Ihre eigenen Cache-Controller zu entwerfen.

Schritt 1: Spezifikationen

Dies sind die wichtigsten Spezifikationen des Cache-Controllers, den wir entwerfen werden:

- Direkt zugeordnet. (Gehen Sie zu diesem Link, wenn Sie nach einem assoziativen zugeordneten Cache-Controller suchen)

- Single-Banked, blockierender Cache.

- Write-Through-Richtlinie für Write-Treffer.

- No-Write-Zuweisungs- oder Write-Around-Richtlinie bei Schreibfehlern.

- Kein Schreibpuffer oder andere Optimierungen.

- Tag-Array ist integriert.

Außerdem werden wir einen Cache-Speicher und ein Hauptspeichersystem entwerfen.

Die (konfigurierbaren) Standardspezifikationen des Cache-Speichers:

- 256 Bytes Single-Banked-Cache.

- 16 Cache-Zeilen, jede Cache-Zeile (Block) = 16 Bytes.

Die Spezifikationen des Hauptspeichers:

- Synchroner Lese-/Schreibspeicher.

- Multi-banked Interleaved Memory - vier Speicherbänke.

- Jede Bankgröße = jeweils 1 kB. Daher Gesamtgröße = 4 kB.

- Wort (4 Bytes) adressierbarer Speicher mit 10-Bit-Adressbus.

- Höhere Bandbreite zum Lesen. Lesedatenbreite = 16 Bytes in einem Taktzyklus.

- Schreibdatenbreite = 4 Bytes.

HINWEIS: Überprüfen Sie mein neueres anweisbares, wenn Sie nach 4-Wege-assoziativem Cache-Controller-Design suchen

Schritt 2: RTL-Ansicht des gesamten Systems

Die vollständige RTL-Darstellung des Top-Moduls ist in der Abbildung dargestellt (ohne Prozessor). Die Standardspezifikationen für die Busse sind:

- Alle Datenbusse sind 32-Bit-Busse.

- Adressbus = 32-Bit-Bus (aber hier sind nur 10 Bits vom Speicher adressierbar).

- Datenblock = 128 Bit (Bus mit breiter Bandbreite zum Lesen).

- Alle Komponenten werden von derselben Uhr angetrieben.

Schritt 3: Testumgebung

Das Top-Modul wurde mit einem Prüfstand getestet, der einfach einen Prozessor ohne Pipeline modelliert (denn einen kompletten Prozessor zu entwerfen ist gar nicht so einfach !!). Der Prüfstand generiert häufig Lese-/Schreibdatenanforderungen an den Speicher. Dies verspottet typische "Load"- und "Store"-Befehle, die in allen von einem Prozessor ausgeführten Programmen gemeinsam sind. Die Testergebnisse haben die Funktionalität des Cache Controllers erfolgreich verifiziert. Im Folgenden sind die beobachteten Teststatistiken aufgeführt:

- Alle Read/Write Miss- und Hit-Signale wurden korrekt generiert.

- Alle Operationen zum Lesen/Schreiben von Daten waren erfolgreich.

- Keine Dateninkohärenz-/Inkonsistenzprobleme festgestellt.

- Das Design wurde erfolgreich für ein Maxm-Timing verifiziert. Taktfrequenz des Betriebs = 110 MHz in Xilinx Virtex-4 ML-403 Board (gesamtes System), 195 MHz für Cache Controller allein.

- Für den Hauptspeicher wurden Block-RAMs abgeleitet. Alle anderen Arrays wurden auf LUTs implementiert.

Schritt 4: Angehängte Dateien

Folgende Dateien sind hier mit diesem Blog angehängt:

- . VHD-Dateien von Cache Controller, Cache Data Array, Hauptspeichersystem.

- Prüfstand.

- Dokumentation zum Cache-Controller.

Anmerkungen:

- Gehen Sie die Dokumentation durch, um die Spezifikationen des hier vorgestellten Cache-Controllers vollständig zu verstehen.

- Alle Änderungen im Code sind von anderen Modulen abhängig. Die Änderungen sollten also mit Bedacht vorgenommen werden. Beachten Sie alle Kommentare und Überschriften, die ich gegeben habe.

- Wenn aus irgendeinem Grund Block-RAMs für den Hauptspeicher nicht abgeleitet werden, REDUZIEREN Sie die Größe des Speichers, gefolgt von Änderungen der Adressbusbreiten über die Dateien hinweg und so weiter. Damit der gleiche Speicher entweder auf LUTs oder Distributed RAM implementiert werden kann. Dies spart Zeit und Ressourcen für das Routing. Oder gehen Sie zur spezifischen FPGA-Dokumentation und suchen Sie den kompatiblen Code für Block-RAM und bearbeiten Sie den Code entsprechend und verwenden Sie die gleichen Adressbusbreitenspezifikationen. Gleiche Technik für Altera FPGAs.

Empfohlen:

So erstellen Sie eine 4G LTE Doppel-BiQuade-Antenne in einfachen Schritten: 3 Schritte

So erstellen Sie eine 4G LTE-Doppel-BiQuade-Antenne Einfache Schritte: Die meiste Zeit, in der ich konfrontiert war, habe ich keine gute Signalstärke für meine täglichen Arbeiten. So. Ich suche und probiere verschiedene Antennentypen aus, aber es funktioniert nicht. Nach verschwendeter Zeit habe ich eine Antenne gefunden, die ich hoffentlich herstellen und testen kann, weil sie vom Bauprinzip nicht

Spielen Sie Doom auf Ihrem iPod in 5 einfachen Schritten!: 5 Schritte

Spielen Sie Doom auf Ihrem iPod in 5 einfachen Schritten!: Eine Schritt-für-Schritt-Anleitung zum Dual-Booten von Rockbox auf Ihrem iPod, um Doom und Dutzende anderer Spiele zu spielen. Es ist wirklich einfach zu tun, aber viele Leute sind immer noch erstaunt, wenn sie sehen, wie ich Doom auf meinem iPod spiele, und werden mit der Anleitung verwirrt

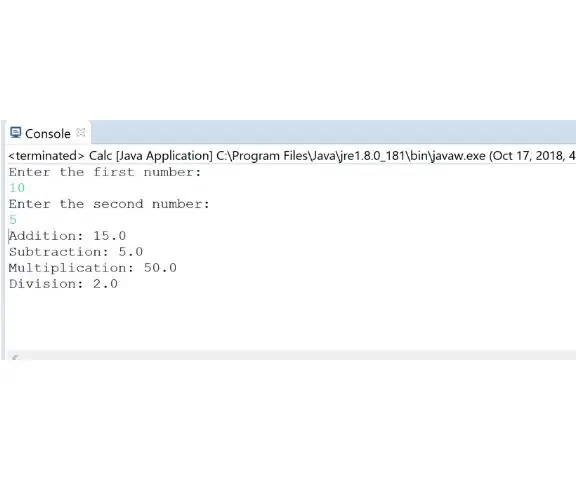

So erstellen Sie einen einfachen Rechner in Java – wikiHow

So erstellen Sie einen einfachen Rechner in Java: Dies ist eine einfache Einführung in die Java-Programmiersprache, die für Personen mit geringen bis keinen Programmierkenntnissen gedacht ist. Materialien: Computer oder Laptop (mit installiertem Eclipse) Kann Eclipse unter https://www. eclipse.org/downloads

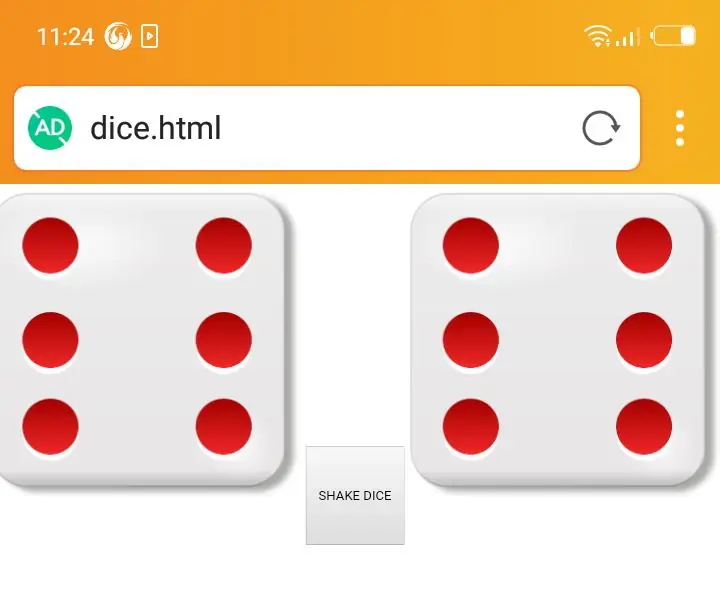

Einen einfachen zufälligen virtuellen Würfel codieren – wikiHow

So codieren Sie einen einfachen virtuellen Zufallswürfel: Hallo zusammen!!!!! Dies ist mein erstes anweisbares und ich werde Ihnen beibringen, wie man einen virtuellen Würfel auf Ihrem PC oder Smartphone codiert. Ich verwende HTML,JavaScript und CSS, ich hoffe, es gefällt euch allen und vergesst nicht, im folgenden Kontext für mich zu stimmen

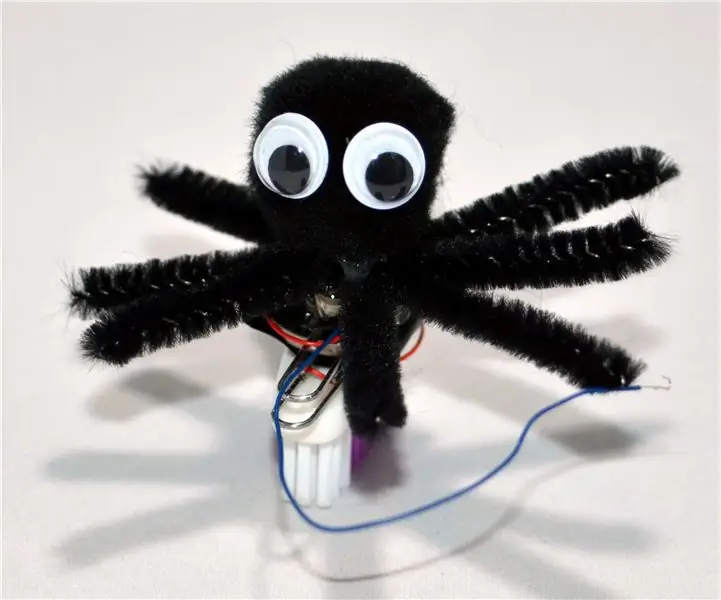

Einen einfachen Spiderbot für Halloween bauen – wikiHow

So bauen Sie einen einfachen Spiderbot für Halloween: Dies ist ein einfacher, lustiger Borstenbot für Halloween! Bristlebots sind großartige Starterprojekte für Leute, die die Grundlagen der Schaltungen und des Roboterbaus erlernen. Mit dem Kopf einer Zahnbürste für den Körper, einem kleinen Motor für die Bewegung und einem Akku