Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:17.

- Zuletzt bearbeitet 2025-06-01 06:08.

Ich bin überwältigt von den Antworten, die ich in diesem Blog bekomme. Danke Leute, dass ihr meinen Blog besucht und mich motiviert habt, mein Wissen mit euch zu teilen. Dieses Mal werde ich das Design eines anderen interessanten Moduls vorstellen, das wir in allen SOCs sehen - Interrupt Controller.

Wir werden einen einfachen, aber leistungsstarken programmierbaren Interrupt-Controller entwickeln. Es handelt sich um ein vollständig konfigurierbares und parametrisiertes Design, das plattformübergreifend portiert werden kann. Ich habe dies entworfen, nachdem ich viel über einige gängige Interrupt-Controller-Architekturen wie NVIC, 8259a, RISC-V PLIC, Microblaze's INTC usw. gelesen habe. Ich hoffe, Sie finden diesen Blog hilfreich und helfen Ihnen, einen Eindruck davon zu bekommen, wie Interrupts von einem Prozessor verarbeitet werden mit Hilfe eines Interrupt-Controllers.

Schritt 1: Spezifikationen

Im Folgenden sind die Spezifikationen der IP:

- AHB3-Lite-Schnittstelle.

-

Statisch konfigurierbare Parameter:

- Anzahl externer Interruptquellen; unterstützt bis zu 63 Interrupts.

- Anzahl der Prioritätsstufen; unterstützt bis zu 63 Stufen.

- Anzahl der Verschachtelungsebenen; unterstützt bis zu 8 Verschachtelungsebenen.

- Busbreite; 32 oder 64.

- Global und lokal maskierbare Interrupts.

- Dynamisch konfigurierbare Prioritätsstufe für jeden Interrupt.

- Zwei Betriebsmodi - Fully Nested Mode und Equal Priority Mode.

- Unterstützt Active-High-Level-sensitive Interrupts.

Im Design wird ein von den RISC-V PLIC-Spezifikationen inspirierter Interrupt-Handshake-Mechanismus verwendet.

Die Unterbrechungspräemption ist inspiriert von 8259a

Andere liest: Microblaze INTC, NVIC

Schritt 2: Übersicht über PIC

Der programmierbare Interrupt-Controller (PIC) empfängt mehrere Interrupts von externen Peripheriegeräten und führt sie zu einem einzigen Interrupt-Ausgang zu einem Zielprozessorkern zusammen.

PIC wird über Steuer- und Statusregister gesteuert. Alle PIC-Register sind speicherabgebildet, und es wird über die AHB3-Lite-Busschnittstelle zugegriffen.

Die Registerbank besteht aus Konfigurationsregistern, Freigaberegistern, schwebenden Registern, In-Service-Registern, Prioritätsregistern und ID-Registern, die typisch für Interrupt-Controller sind.

Das Konfigurationsregister wird verwendet, um den Betriebsmodus des PIC einzustellen. Es kann entweder im vollständig verschachtelten Modus oder im Modus mit gleicher Priorität arbeiten.

Jedem Interrupt können Prioritäten zugewiesen und individuell maskiert werden. Auch die globale Maskierung aller Interrupts wird unterstützt.

Die Registerbank interagiert mit dem Priority Resolver und BTC (Binary-Tree-Comparator), um die Prioritäten anstehender Interrupts aufzulösen und dem Prozessor entsprechend Interrupts geltend zu machen. Das ID-Register enthält die ID des anstehenden Interrupts mit der höchsten Priorität.

Schritt 3: RTL-Design und -Implementierung

Beim Design von PIC liegt der Schwerpunkt auf der Reduzierung der Latenz beim Auflösen von Prioritäten, was der zeitkritischste Teil des Designs ist. Da das Design Prioritäten in einem einzigen Taktzyklus auflöst, verschlechtert sich die Leistung mit der Zunahme der Anzahl von Quellen mit einer Log2-Komplexität.

Das Design wurde erfolgreich implementiert und das Timing bis zu den folgenden Frequenzen auf Artix-7-FPGAs verifiziert.

- Bis zu 15 Quellen: 100 MHz

- Bis zu 63 Quellen: 50 MHz

Die Interrupt-Latenz, die allein durch PIC hinzugefügt wird, beträgt 3 Taktzyklen (mit Ausnahme der Kontextwechselzeit des Prozessors und der ersten ISR-Befehlsabrufzeit).

Schritt 4: Wichtige Hinweise und angehängte Dateien

Wichtige Notizen:

- Wenn die AHB3-Lite-Schnittstelle unerwünscht ist, können Sie das obere Modul wechseln und das Skelettdesign von PIC verwenden. Der mitgelieferte Prüfstand ist jedoch für IP mit AHB3-Lite Interface.

- PIC IP v1.0 ist ein vollständig tragbares, reines RTL-Design.

- Funktionell überprüft, um in beiden Modi zu funktionieren.

Angehängte Dokumente:

- Entwerfen Sie Codes und Testbench in VHDL.

- Vollständige IP-Dokumentation.

Es ist ein Open-Source-Design … Fühlen Sie sich frei zu verwenden …

Bei Rückfragen jederzeit:

Mitu Raja

Empfohlen:

3D-Druck eines Roboters – wikiHow

Wie man einen Roboter in 3D druckt: Heute zeige ich Ihnen, wie Sie von einer in wenigen Minuten erstellten Skizze zu einem gut aussehenden professionellen Roboter gelangen, der druckfertig ist

Die Kurzanleitung zum Erstellen eines Videos mit Ihrem IPhone und Hochladen auf Facebook oder YouTube: 9 Schritte

Die Kurzanleitung zum Erstellen eines Videos mit Ihrem IPhone und Hochladen auf Facebook oder YouTube: Verwenden Sie diesen einfachen 5-Schritte-Prozess (Instructables lässt es wie mehr Schritte aussehen, als es tatsächlich ist), um Ihr erstes YouTube- oder Facebook-Video zu erstellen und hochzuladen - mit nur dein iPhone

Verbinden eines GPS-Moduls mit dem Raspberry Pi: Dashcam Teil 2: 3 Schritte

Anbindung eines GPS-Moduls an den Raspberry Pi: Dashcam Teil 2: Dies ist Teil 2 des Dashcam-Projekts und in diesem Beitrag erfahren Sie, wie Sie ein GPS-Modul an den Raspberry Pi anschließen. Wir verwenden dann die GPS-Daten und fügen sie dem Video als Textüberlagerung hinzu. Bitte lesen Sie Teil 1 über den untenstehenden Link, bevor Sie

Erstellen eines Blogs mit Blogger.com – wikiHow

Erstellen eines Blogs mit Blogger.com: Die folgenden Anweisungen zeigen Ihnen, wie Sie mit Blogger.com ein Blog erstellen. Sie benötigen eine Google-E-Mail-Adresse, um Blogger.com zu verwenden

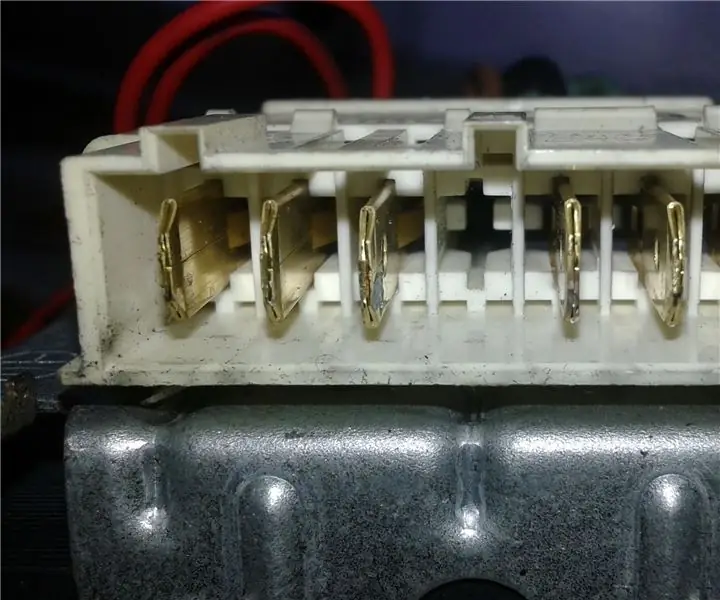

So finden Sie die Stifte eines Waschmaschinenmotors – wikiHow

So finden Sie die Pins eines Waschmaschinenmotors: Finden Sie die Pins eines Waschmaschinenmotors mit Hilfe eines digitalen Multimeters. Wir benötigen ein Multimeter im Durchgangsprüfermodus und einen ähnlichen universellen Waschmaschinenmotor wie im Bild oben. Wir werden Beginnen Sie zunächst mit einer Sichtprüfung des