Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:16.

- Zuletzt bearbeitet 2025-01-23 12:52.

In diesem Instructable beschreiben wir, wie man einen 8-Bit-Analog-Digital-Wandler (ADC) im SLG46855V implementiert, der den Laststrom erfassen und über I2C mit einer MCU verbinden kann. Dieses Design kann für verschiedene Strommessanwendungen wie Amperemeter, Fehlererkennungssysteme und Kraftstoffanzeigen verwendet werden.

Im Folgenden haben wir die erforderlichen Schritte beschrieben, um zu verstehen, wie die Lösung programmiert wurde, um die ADC-Strommessung zu erzeugen. Wenn Sie jedoch nur das Ergebnis der Programmierung erhalten möchten, laden Sie die GreenPAK-Software herunter, um die bereits fertige GreenPAK-Designdatei anzuzeigen. Schließen Sie das GreenPAK Development Kit an Ihren Computer an und klicken Sie auf das Programm, um die ADC-Strommessung zu erstellen.

Schritt 1: ADC-Architektur

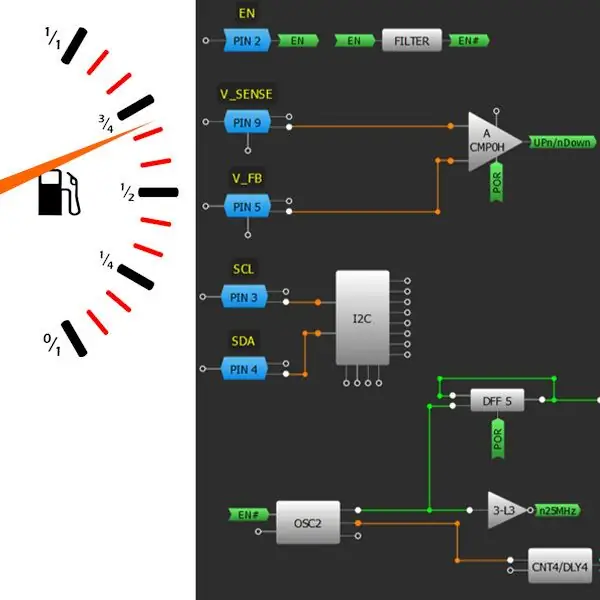

Der ADC besteht im Wesentlichen aus einem analogen Komparator und einem Digital-Analog-Wandler (DAC). Der Komparator misst die Eingangsspannung gegenüber der DAC-Ausgangsspannung und steuert anschließend, ob der DAC-Eingangscode inkrementiert oder dekrementiert wird, so dass der DAC-Ausgang zur Eingangsspannung konvergiert. Der resultierende DAC-Eingangscode wird der digitale ADC-Ausgangscode.

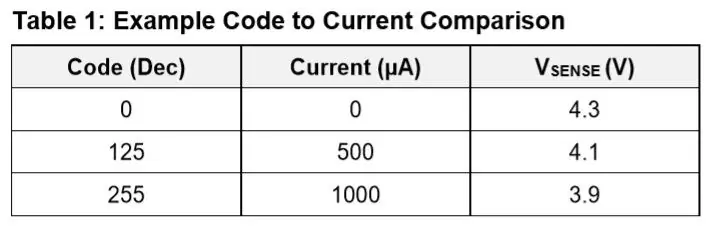

In unserer Implementierung erstellen wir einen DAC mit einem durch Pulsweitenmodulation (PWM) gesteuerten Widerstandsnetzwerk. Mit GreenPAK können wir ganz einfach einen präzisen digital gesteuerten PWM-Ausgang erstellen. Die gefilterte PWM wird zu unserer analogen Spannung und dient somit als effektiver DAC. Ein deutlicher Vorteil dieses Ansatzes besteht darin, dass es einfach ist, die Spannungen einzustellen, die dem Nullcode und dem Vollausschlag (entsprechend Offset und Verstärkung) entsprechen, indem einfach die Widerstandswerte angepasst werden. Zum Beispiel möchte ein Benutzer idealerweise den Nullcode von einem Temperatursensor ohne Strom (0 µA) entsprechend 4,3 V und den Full-Scale-Code bei 1000 µA entsprechend 3,9 V lesen (Tabelle 1). Dies ist einfach durch Einstellen einiger Widerstandswerte zu implementieren. Indem der ADC-Bereich mit dem interessierenden Sensorbereich übereinstimmt, nutzen wir die ADC-Auflösung optimal aus.

Eine Designüberlegung für diese Architektur besteht darin, dass eine interne PWM-Frequenz viel schneller sein muss als die ADC-Aktualisierungsrate, um ein unterdämpftes Verhalten seines Regelkreises zu verhindern. Zumindest sollte er länger sein als der ADC-Datenzählertakt geteilt durch 256. In diesem Design ist die ADC-Aktualisierungsperiode auf 1,3312 ms eingestellt.

Schritt 2: Interner Stromkreis

Der flexible ADC basiert auf dem Design von Dialog Semiconductor AN-1177. Der Takt wird von 1 MHz auf 12,5 MHz erhöht, um den ADC-Zähler zu takten, da das SLG46855 über 25 MHz Takt verfügt. Dies ermöglicht eine viel schnellere Aktualisierungsrate für eine feinere Probenauflösung. Die LUT, die den ADC-Datentakt taktet, wird so geändert, dass sie das 12,5-MHz-Signal durchläuft, wenn der PWM-DFF niedrig ist.

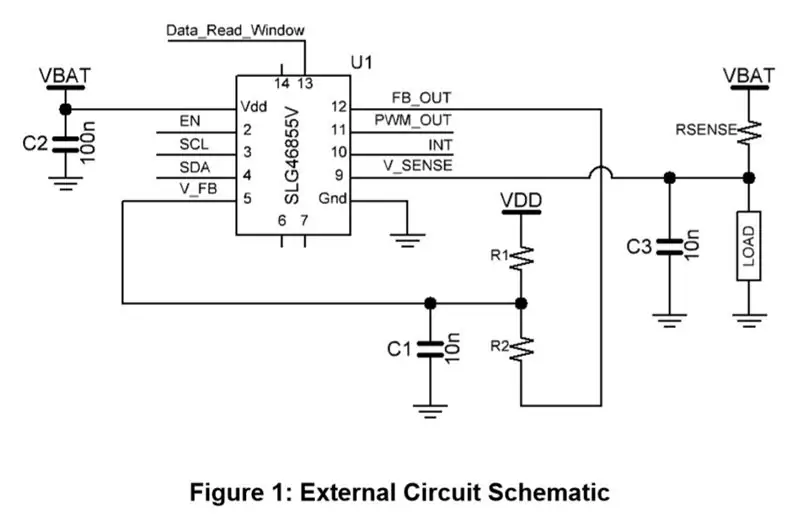

Schritt 3: Externe Schaltung

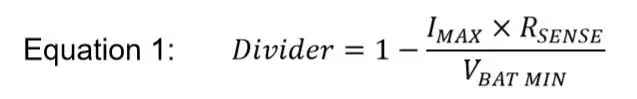

Ein externes Widerstands- und Kondensatornetzwerk wird verwendet, um eine PWM in eine analoge Spannung umzuwandeln, wie im Schaltplan in Abbildung 1 gezeigt. Die Werte werden für die maximale Auflösung für den maximalen Strom berechnet, den das Gerät erfasst. Um diese Flexibilität zu erreichen, fügen wir die Widerstände R1 und R2 parallel zu VDD und Masse hinzu. Ein Widerstandsteiler teilt VBAT auf die untere Seite des Spannungsbereichs herunter. Das Teilerverhältnis für eine erwartete minimale VBAT kann mit der Gleichung 1 gelöst werden.

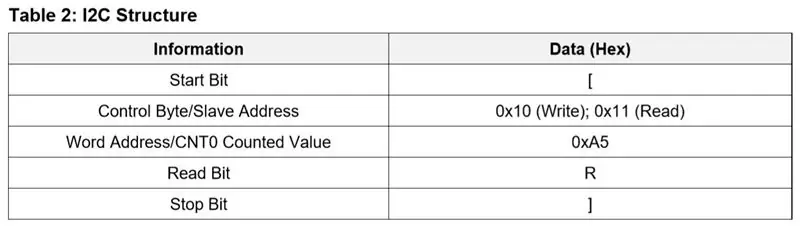

Schritt 4: Anweisungen zum Lesen von I2C

Tabelle 1 beschreibt die I2C-Befehlsstruktur zum Zurücklesen der in CNT0 gespeicherten Daten. Die I2C-Befehle erfordern ein Startbit, ein Steuerbyte, eine Wortadresse, ein Lesebit und ein Stoppbit.

Ein Beispiel für einen I2C-Befehl zum Zurücklesen des CNT0-Zählwerts ist unten geschrieben:

[0x10 0xA5] [0x11 R]

Der zurückgelesene gezählte Wert ist der ADC-Codewert. Als Beispiel ist ein Arduino-Code in der ZIP-Datei dieser Application Note auf der Website von Dialog enthalten.

Schritt 5: Ergebnisse

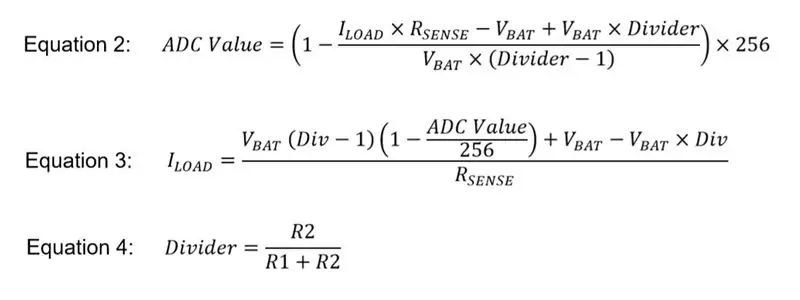

Um die Genauigkeit des ADC-Stromerfassungsdesigns zu testen, wurden die gemessenen Werte bei einem gegebenen Laststrom und VDD-Pegel mit einem theoretischen Wert verglichen. Die theoretischen ADC-Werte wurden mit der Gleichung 2 berechnet.

Die ILOAD, die mit einem ADC-Wert korreliert, wird mit der Gleichung 3 gefunden.

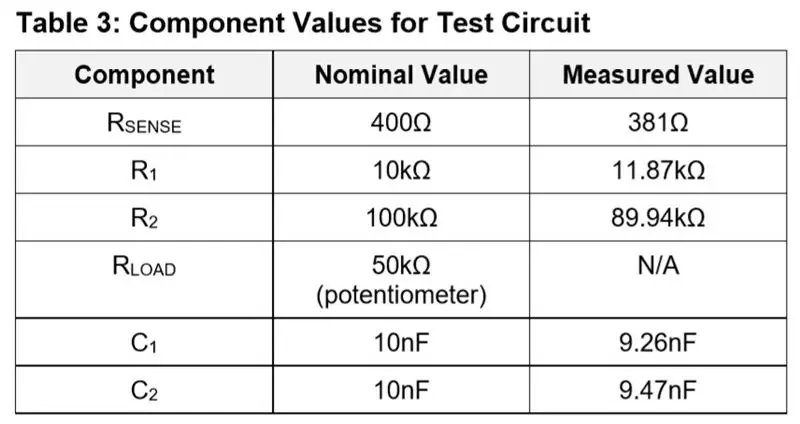

Für die folgenden Ergebnisse habe ich diese in Tabelle 3 gezeigten Komponentenwerte verwendet.

Die Auflösung der Umwandlung von ADC-Wert in ILOAD kann berechnet werden, indem Gleichung 3 mit den gemessenen Werten in Tabelle 2 und dem ADC-Wert auf 1 gesetzt wird. Bei einer VBAT von 3,9 V beträgt die Auflösung 4,96 µA/div.

Um die ADC-Strommessschaltung auf einen minimalen VDD-Pegel von 3,6 V mit einem maximalen Strom von 1100 µA und einem Messwiderstand von 381 zu optimieren, wäre der ideale Teilerkoeffizient 0,884, basierend auf Gleichung 1. Mit den in Tabelle. angegebenen Werten 2 hat der tatsächliche Teiler einen Teilerkoeffizienten von 0,876. Da dies etwas weniger ist, ermöglicht dies einen etwas größeren Laststrombereich, sodass die ADC-Werte nahe am vollen Bereich liegen, aber nicht überlaufen. Der tatsächliche Teilerwert wird mit der Gleichung 4 berechnet.

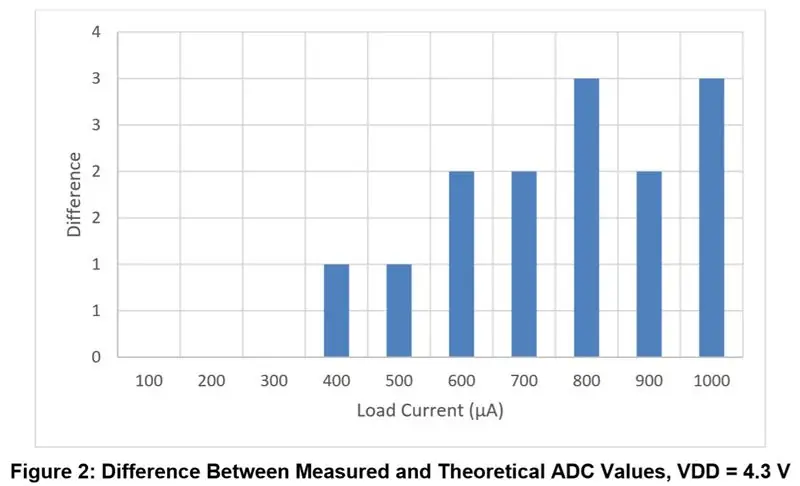

Oben (Abbildungen 2-6, Tabellen 4-6) sind die Messungen der Schaltung bei drei Spannungspegeln aufgeführt: 4,3 V, 3,9 V und 3,6 V. Jeder Pegel zeigt ein Diagramm an, das die Differenz zwischen den gemessenen und den theoretischen ADC-Werten anzeigt. Theoretische Werte werden auf die nächste ganze ganze Zahl gerundet. Es gibt ein zusammenfassendes Diagramm, um die Unterschiede auf den drei Spannungsniveaus zu vergleichen. Danach gibt es eine Grafik, die die Korrelation zwischen den theoretischen ADC-Werten und dem Laststrom bei den verschiedenen Spannungsniveaus anzeigt.

Abschluss

Das Gerät wurde auf drei Spannungsniveaus getestet: 3,6 V, 3,9 V und 4,3 V. Der Bereich dieser Spannungen modelliert eine vollständige Lithium-Ionen-Batterie, die sich bis zu ihrem Nennwert entlädt. Von den drei Spannungspegeln wurde beobachtet, dass das Gerät typischerweise bei 3,9 V für den gewählten externen Stromkreis genauer war. Der Unterschied zwischen gemessenen und theoretischen ADC-Werten betrug bei Lastströmen von 700 - 1000 µA nur 1 Dezimalwert. Im angegebenen Spannungsbereich lagen die gemessenen ADC-Werte im schlimmsten Fall 3 Dezimalpunkte über den Nennbedingungen. Weitere Anpassungen des Widerstandsteilers können vorgenommen werden, um verschiedene VDD-Spannungspegel zu optimieren.

Empfohlen:

Machen Sie Ihren eigenen USB-Lüfter - Englisch / Französisch: 3 Schritte

Machen Sie Ihren eigenen USB-Lüfter | English / Francais: DEUTSCH Heute habe ich auf Websites gesehen, dass wir USB-Lüfter kaufen können. Aber ich habe gesagt, warum ich nicht meins machen soll? Was Sie brauchen: - Klebeband Elektriker oder Entenband - Ein PC-Lüfter - Ein USB-Kabel, das Ihnen nicht dient - Einen Drahtschneider - Einen Schraubendreher - Eine Saitenmuschel

Ernie machen – wikiHow

How to Make Ernie: Dies ist ein Tutorial zum Bauen von Ernie, Ihrem autonomen Sound-Following-Roboter, mit einem Zybo-Board. Es wird behandelt, wie Sie: ein Projekt in Vivado erstellen, PWM-ähnliche Servomotortreiber im FPGA erstellen, eine Schnittstelle zu zwei Schallsensoren erstellen, eine Ti

Ein Spongebob-Ananas-Haus machen – wikiHow

Wie man ein Spongebob-Ananas-Haus macht: Wer lebt in einer Ananas unter dem Meer? Die Antwort auf diese Frage (Spongebob) ist für die meisten Menschen heute ziemlich offensichtlich. Unser Team wurde damit beauftragt, eine Requisite für die kommende Theaterproduktion zu entwerfen und zu bauen. Die Idee, die sofort kam

Anständige Musik digital machen – wikiHow

Wie man anständige Musik digital macht: Wenn Sie Musik auf einem computerbasierten Gerät (iPad, iPhone, MacBook, Laptop, Computer usw.) machen, müssen Sie mehrere Dinge beachten. Erstens müssen Sie sich für ein D.A.W. (Auch bekannt als digitale Audio-Workstation), um Musik zu machen oder zu produzieren.Se

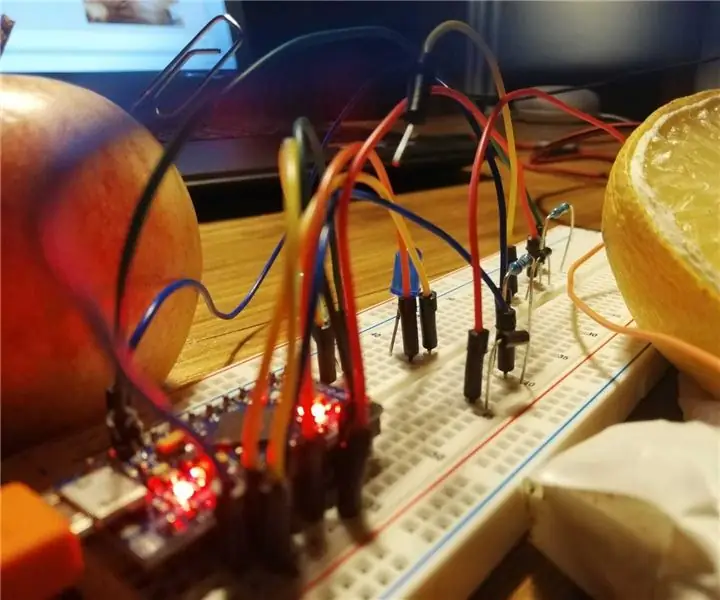

Kein Makey Makey? Keine Probleme ! So machen Sie Ihren Makey Makey zu Hause: 3 Schritte

Kein Makey Makey? Keine Probleme ! So machen Sie Ihr Makey Makey zu Hause!: Wollten Sie schon immer am Makey Makey-Wettbewerb für Instructables teilnehmen, aber Sie hatten noch nie einen Makey Makey?! JETZT können Sie! Mit der folgenden Anleitung möchte ich Ihnen zeigen, wie Sie mit einigen einfachen Komponenten, die Sie b