Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:17.

- Zuletzt bearbeitet 2025-01-23 12:52.

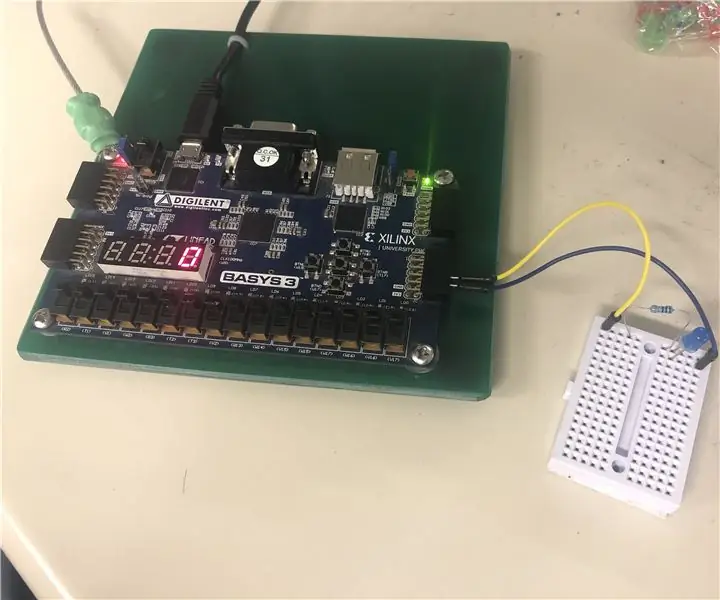

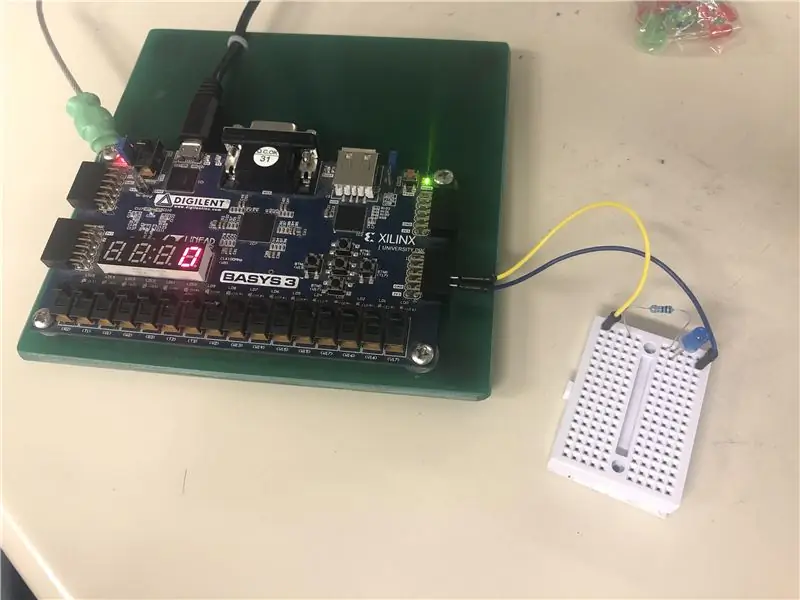

In dieser Anleitung bauen und steuern wir ein externes LED-Dimmsystem. Mit den verfügbaren Tasten kann der Benutzer die LED-Lampe auf jede gewünschte Helligkeit dimmen. Das System verwendet die Basys 3-Platine und ist mit einem Steckbrett verbunden, das einen Widerstand und die LED-Lampe enthält. Durch Drücken der dafür vorgesehenen "Auf"-Taste wird die Helligkeit erhöht und durch Drücken der "Ab"-Taste wird die Helligkeit bis auf Null verringert. Dies verhindert nicht nur, dass der Benutzer durch sonnenhelle Glühbirnen geblendet wird, sondern spart auch Energie!

Schritt 1: Eingabezähler erstellen

Für diesen Schritt erstellen wir die Komponente, die die Helligkeit (durch eine Uhr) bestimmt, indem wir zwei Schalter verwenden: einen zum Erhöhen und einen zum Verringern. Mit VHDL haben wir den Zähler durch die Verwendung von D-Flip-Flops erzeugt. Durch Drücken der "Auf"-Taste wird der nächste Zustand in den aktuellen Zustand verschoben und auf die Siebensegmentanzeige und die LED-Lampe ausgegeben.

Entität updown_counter ist

Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_enable: in STD_LOGIC; up_enable: in STD_LOGIC; updown_counter beenden; Architektur Verhalten von updown_counter ist begin flop: process(next_state, clk, up_enable, down_enable, previous_state) begin if (rising_edge(clk)) then if (up_enable = '1' and not(next_state="0000")) then present_state <= next_state; elsif (down_enable = '1' und nicht(vorheriger_zustand = "1111")) then present_state <= previous_state; Ende, wenn; Ende, wenn; Prozessflop beenden; Ende Verhalten;

Wir brauchen auch einen Takt für jeden Eingang, der (wenn er ansteigt) verriegelt werden soll, also haben wir auch einen Taktteiler erstellt, der bestimmt, wie schnell die Tasten zwischen den einzelnen Helligkeitsstufen gedrückt werden können. Dieser Taktteiler ermöglicht es uns, den richtigen Pegel auf der Sieben-Segment-Anzeige richtig anzuzeigen und für jeden Pegel den richtigen Intensitätspegel zu erzeugen.

Entität counter_clkDiv ist

Port (clk: in std_logic; sclk: out std_logic); end counter_clkDiv; Architektur my_clk_div von counter_clkDiv ist konstant max_count: integer:= (10000000); Signal tmp_clk: std_logic:= '0'; begin my_div: Prozess (clk, tmp_clk) Variable div_cnt: Ganzzahl:= 0; begin if (rising_edge(clk)) then if (div_cnt >= MAX_COUNT) then tmp_clk <= nicht tmp_clk; div_cnt:= 0; sonst div_cnt:= div_cnt + 1; Ende, wenn; Ende, wenn; sclk <= tmp_clk; Prozess beenden my_div; end my_clk_div;

Schritt 2: LED Clock Divider erstellen

Für diesen Schritt erstellen wir einen Taktteiler für die LED-Lampe, um 16 verschiedene Intensitätsstufen zu bestimmen. Da 0 bis 15 ausgeschaltet ist und die maximale Helligkeit anzeigt, erhöht der Taktteiler jeden Tastendruck um die von uns eingestellten Helligkeitsstufen. Jede ansteigende Stufe bedeutete eine Erhöhung des Takts für die LED-Lampe. Da die Helligkeit nicht linear ansteigt, haben wir die Uhr auf den höchsten Wert gedreht und unsere Uhren entsprechend verringert.

Hinweis: Wir verwenden eine blaue LED. Die Verwendung einer anderen Farbe (wie Rot) erfordert insgesamt etwas andere Uhren; eine mittlere Helligkeitseinstellung für Blau könnte bereits die maximale Helligkeit für Rot sein. Dies geschieht, weil unterschiedliche Lichtwellenlängen unterschiedliche Energiemengen erfordern, wobei die kühleren Farben wie Lila und Blau mehr Energie benötigen, während die wärmeren Farben wie Rot und Orange weniger Energie benötigen.

Entität led_clkDiv ist Port (present_state: in STD_LOGIC_VECTOR (3 bis 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); end led_clkDiv; Architektur Verhalten von led_clkDiv ist Signal tmp_clk: std_logic:= '0'; Shared Variable max_count: integer;begin count_stuff: Prozess (present_state) begin case present_state ist wenn "0000" => max_count:= 0; wenn "0001" => max_count:= 2; wenn "0010" => max_count:= 4; wenn "0011" => max_count:= 6; wenn "0100" => max_count:= 8; wenn "0101" => max_count:= 10; wenn "0110" => max_count:= 12; wenn "0111" => max_count:= 14; wenn "1000" => max_count:= 16; wenn "1001" => max_count:= 25; wenn "1010" => max_count:= 50; wenn "1011" => max_count:= 100; wenn "1100" => max_count:= 150; wenn "1101" => max_count:= 200; wenn "1110" => max_count:= 250; wenn "1111" => max_count:= 300; Endfall; endprozess count_stuff; my_div: Prozess (clk, tmp_clk, present_state) Variable div_cnt: Ganzzahl:= 0; begin if (rising_edge(clk)) then if (div_cnt >= max_count) then tmp_clk <= nicht tmp_clk; div_cnt:= 0; sonst div_cnt:= div_cnt + 1; Ende, wenn; Ende, wenn; led_clk <= tmp_clk; Prozess beenden my_div; Ende Verhalten;

Schritt 3: Erstellen des LED-Controllers

Jetzt, wo wir es so weit geschafft haben, ist es an der Zeit, alle bisher erstellten Komponenten in der LED-Controller-Datei zusammenzufassen.

Zusammenfassend sind die verwendeten Komponenten die folgenden:

- Eingangszähler (updown_counter)

- Taktteiler (counter_clkDiv)

- LED-Taktteiler (led_clkDiv)

- Sieben-Segment-Anzeigentreiber (sseg_dec) (angehängte Datei)

Der Sieben-Segment-Anzeigetreiber wurde zuvor nicht diskutiert, da wir die VHDL-Datei aufgrund ihres langen und komplizierten Codes tatsächlich von Dr. Bryan Mealy ausgeliehen haben. Im Wesentlichen steuert es unsere Tasteneingaben auf die Sieben-Segment-Anzeige auf dem Basys 3-Board, damit wir wissen, welche Helligkeitsstufe eingeschaltet ist.

Im weiteren Verlauf verwendet der LED-Controller Flip-Flops, um die Zählung zu erhöhen oder zu verringern, die sowohl die Siebensegmentanzeige als auch die Helligkeit der LED-Lampe gleichzeitig steuert.

Entity Counter ist Port (clk: in STD_LOGIC; up_enable: in STD_LOGIC; down_enable: in STD_LOGIC; SEGMENTS: out STD_LOGIC_VECTOR (7 downto 0); DISP_EN: out STD_LOGIC_VECTOR (3 downto 0); led_clk: out STD_LOGIC); Endzähler; Architektur Verhalten des Zählers ist Komponente updown_counter ist Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_enable:in; up_enable: in STD_LOGIC); Endkomponente updown_counter; Komponente counter_clkDiv ist Port (clk: in std_logic; sclk: out std_logic); Endkomponente counter_clkDiv; Komponente sseg_dec ist Port (ALU_VAL: in std_logic_vector(7 downto 0); SIGN: in std_logic; VALID: in std_logic; CLK: in std_logic; DISP_EN: out std_logic_vector(3 downto 0); SEGMENTS: out std_logic;; Endkomponente sseg_dec; Komponente led_clkDiv ist Port (present_state: in STD_LOGIC_VECTOR (3 bis 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); Endkomponente led_clkDiv; signal present_state: STD_LOGIC_VECTOR (3 downto 0):= "0000"; signal next_state: STD_LOGIC_VECTOR (3 downto 0):= "0000"; Vorheriger_Zustand signalisieren: STD_LOGIC_VECTOR (3 bis 0):= "0000"; Signal Alu_Val: STD_LOGIC_VECTOR (7 bis 0); Signal sclk: STD_LOGIC; beginnen Alu_Val(7 bis 4) <= "0000"; Alu_Val(3 bis 0) <= gegenwärtiger_Zustand; next_state(0) <= not(present_state(0)); next_state(1) <= present_state(0) xor present_state(1); next_state(2) <= (present_state(0) und present_state(1)) xor present_state(2); next_state(3) <= (present_state(0) und present_state(1) und present_state(2)) xor present_state(3); vorheriger_Zustand(0) <= nicht(gegenwärtiger_Zustand(0)); vorheriger_Zustand(1) <= gegenwärtiger_Zustand(0) xnor gegenwärtiger_Zustand(1); vorheriger_Zustand(2) <= (gegenwärtiger_Zustand(0) noch gegenwärtiger_Zustand(1)) xor gegenwärtiger_Zustand(2); previous_state(3) sclk, next_state => next_state, previous_state => previous_state, up_enable => up_enable, down_enable => down_enable, present_state => present_state); Anzeige: sseg_dec port map(ALU_VAL => Alu_Val, SIGN => '0', VALID => '1', CLK => clk, DISP_EN => DISP_EN, SEGMENTS => SEGMENTS); led_div: led_clkDiv-Port-Map (clk => clk, present_state => Present_state, led_clk => led_clk); clk_div: counter_clkDiv-Port-Map (clk => clk, sclk => sclk); Ende Verhalten;

Schritt 4: Festlegen von Einschränkungen und Montage

Einschränkungen

Um das Basys 3-Board richtig einzurichten und zu programmieren, müssen wir zuerst unsere Constraint-Datei einrichten, die diesem Schritt beigefügt ist. Folgende Einstellungen wurden angepasst:

Tasten

- T18 auf "up_enable" geändert (Helligkeit erhöhen)

- U17 auf "down_enable" geändert (Helligkeit verringern)

7-Segment-Anzeige

- W7, W6, U8, V8, U5, V5, U7, V7 repräsentieren jedes Segment einer Anzeige

- U2, U4, V4, W4 stellen jede angezeigte Anode dar (nur 2 sind aktiv, da unsere höchste Zahl 15 ist)

PMOD-Header JC

JC7 ist, wo wir einen der Drähte der LED-Lampe anschließen, und der andere Draht führt zu GROUND

Nachdem Sie dies alles eingerichtet haben, müssen Sie nur noch Ihren Bitstream generieren (mit jeder Software, die Sie verwenden, z. B. Vivado), Ihr Board programmieren und Boom! Du hast dir ein Arbeitsbrett besorgt.

Hinweis: Die Pinbelegung finden Sie auf dem Basys 3 Datenblatt hier.

Montage

Schritt 5: Verwenden Ihres Dimmerschalters

Wenn alles gut geht, sollten Sie ein voll funktionsfähiges Dimmersystem haben. Zusammenfassend lässt sich sagen, dass durch Drücken der oberen Taste die Helligkeit erhöht wird (bis auf 15), und durch Drücken der unteren Taste wird die Helligkeit verringert (bis auf 0). Hoffentlich geht alles gut für Ihr jetzt entspanntes Sehvermögen!

Empfohlen:

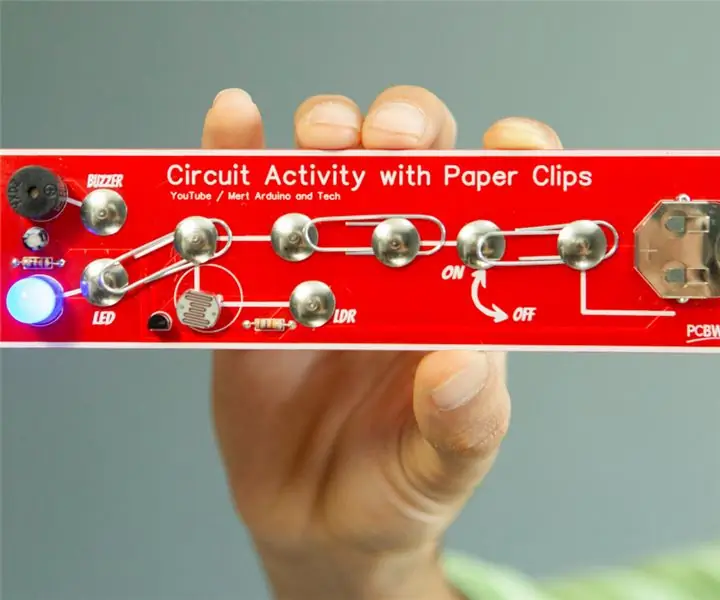

DIY Circuit Activity Board mit Büroklammern - HERSTELLER - STEM: 3 Schritte (mit Bildern)

DIY Circuit Activity Board mit Büroklammern | HERSTELLER | STEM: Mit diesem Projekt können Sie den Weg des elektrischen Stroms ändern, um durch verschiedene Sensoren zu laufen. Mit diesem Design können Sie zwischen dem Aufleuchten einer blauen LED oder dem Aktivieren eines Summers wechseln. Sie haben auch die Wahl, einen lichtabhängigen Widerstand mit

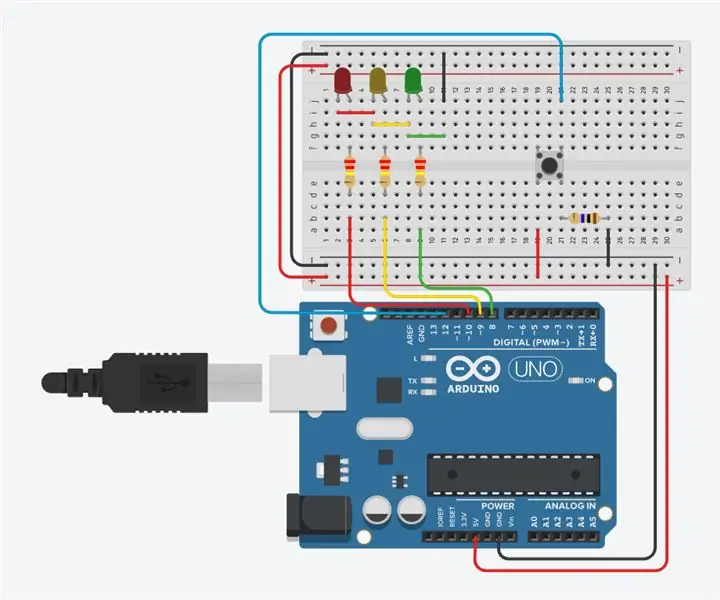

So erstellen Sie eine funktionierende Ampel mit einem Auduino-Board – wikiHow

So erstellen Sie eine funktionierende Ampel mit einem Auduino-Board: Ampeln sind Signalgeräte, die häufig an Straßenkreuzungen, Fußgängerüberwegen und anderen Orten verwendet werden, um den Verkehrsfluss zu steuern. Eine handbetätigte Gasampel war die erste ihrer Art und die Technologie hat die Si

So erstellen Sie eine Message Board-Website mit PHP und MYSQL – wikiHow

So erstellen Sie eine Message Board-Website mit PHP und MYSQL: Diese Anleitung zeigt Ihnen, wie Sie eine Message Board-Website mit PHP, MySQL, HTML und CSS erstellen. Wenn Sie neu in der Webentwicklung sind, machen Sie sich keine Sorgen, es gibt detaillierte Erklärungen und Analogien, damit Sie die Konzepte besser verstehen. Matte

Multisensor-Board Arduino! (Teil1): 11 Schritte (mit Bildern)

Multisensor-Board Arduino! (Teil1): Dieses Board ist eine vollständige Arbeit, die Ihnen hilft, die Messwerte von verschiedenen Sensoren zu erhalten! Bitte besuchen Sie meinen Kanal, Abonnieren: www.youtube.com/user/josexers

Projekt C=BOARD: 5 Schritte (mit Bildern)

Projekt C=BOARD: Das Ziel dieses Projekts ist es, einen Commodore 64-Computer so zu modifizieren, dass er nicht nur ein Computer ist, sondern auch ein rockiges Musikinstrument. Ich möchte den folgenden Leuten danken, die dies möglich gemacht haben:Nak - For sein Paddeldesign (obwohl es ein wir war