Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:15.

- Zuletzt bearbeitet 2025-01-23 12:52.

In diesem Tutorial werden wir den FPGA verwenden, um eine externe LED-Schaltung zu steuern. Folgende Aufgaben werden wir umsetzen

(A) Verwenden Sie die Drucktasten des FPGA Cyclone IV DuePrologic, um die LED zu steuern.

(B) Blinkt LED periodisch ein und aus

Videodemo

Labormenü:

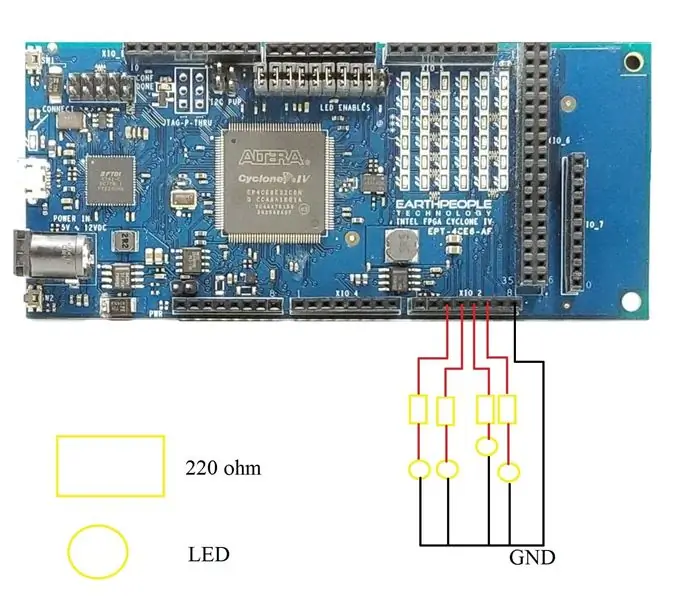

Schritt 1: Elektronische Schaltung aufbauen

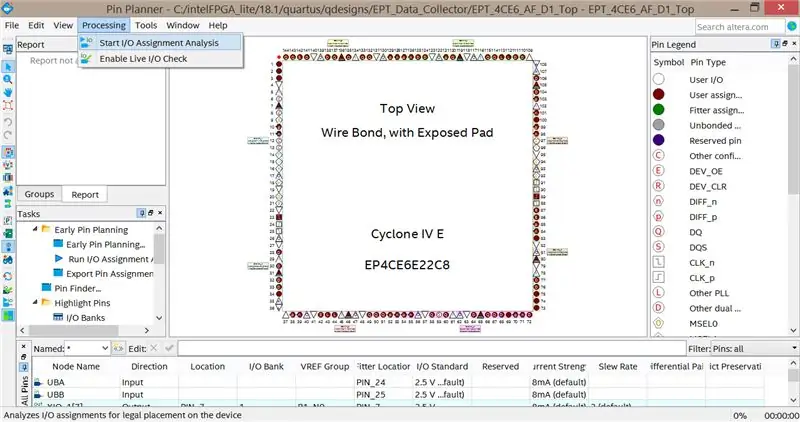

Schritt 2: Überprüfen Sie den Pin-Planer und bearbeiten Sie den Verilog-Code

Schritt 3: Verilog-Code bearbeiten

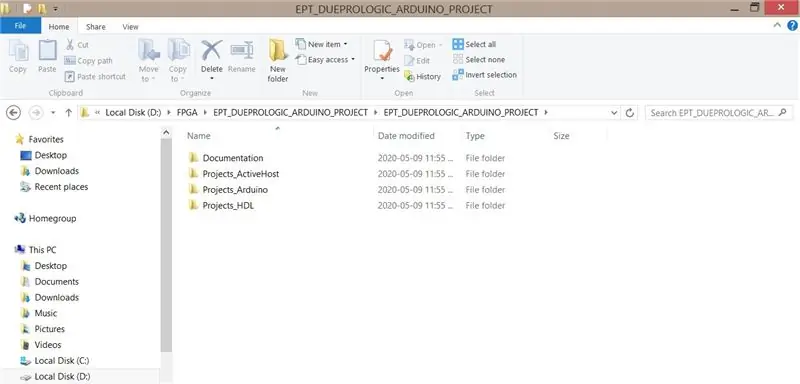

Wenn Sie FPGA DueProLogic kaufen, sollten Sie eine DVD erhalten. Nachdem Sie "Projects_HDL" geöffnet haben, sollten Sie die ursprüngliche Codedatei sehen

Fügen Sie den markierten Code hinzu. Es registriert die I/O-Ports und weist den Ports Nummern zu.

Ausgangsleitung [7:0] XIO_1, //XIO -- D2-D9

Ausgangsleitung [5:0] XIO_2, //XIO -- D10-D12

Ausgangsleitung [5:0] XIO_3, //XIO -- D22-D29

Eingangsleitung [5:0] XIO_4, //XIO -- D30-D37

Eingangsleitung [5:0] XIO_5, //XIO -- D38-D45

Ausgangsleitung [4:0] XIO_6_OUT, //XIO -- D46-D53

Eingangsleitung [31:5] XIO_6, //XIO -- D46-D53

Ausgangsleitung [2:0] XIO_7, //XIO -- D69, D70, D71, D74, D75, D76

Eingangskabel UBA, // Drucktastenschalter

Eingangsdraht UBB // Drucktastenschalter

zuweisen XIO_1[3] = start_stop_cntrl;

zuweisen XIO_2[1] = start_blinky; // LED-Blitz-LED an und aus

zuweisen XIO_2[2] = 1'b1; // Ausgang HIGH

zuweisen XIO_2[3] = ~UBA; //Taste A. drücken

zuweisen XIO_2[4] = UBB; //Taste B. drücken

c_enable zuweisen = XIO_5[2];

zuweisen LEDExt = XIO_5[5];

Dann müssen wir einen Verzögerungstimer einstellen. Kommentieren Sie den ursprünglichen Timer-Code und schreiben Sie eine neue Timer-Funktion

//-----------------------------------------------

// LED Blinky start

//-----------------------------------------------

/*

immer @(posege CLK_66 oder negge RST)

Start

wenn(!RST)

start_blinky <= 1'b0;

anders

Start

if(control_register[7:4] > 0)

start_blinky <= 1'b1;

anders

start_blinky <= 1'b0;

Ende

Ende

*/

reg [31:0] ex;

anfänglicher Anfang

ex <= 32'b0;

start_blinky <= 1'b0;

Ende

immer @(posege CLK_66)

Start

ex <= ex + 1'b1;

if (ex > 1000000000) // Blitz ein/aus ~ 1,6 Sekunden, Takt 66MHz

Start

start_blinky <= !start_blinky;

ex <= 32'b0;

Ende

Ende

//-----------------------------------------------

// LED-Verzögerungs-Timer-Zähler

//-----------------------------------------------

/*

immer @(posege CLK_66 oder negge RST)

Start

wenn(!RST)

led_delay_counter <= TIMER_LOW_LIMIT;

anders

Start

if(state[SELECT_MODE])

led_delay_counter <= Timer_Wert;

sonst if(state[WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

Ende

Ende*/

Schritt 4: Verilog-Code kompilieren

Drücken Sie in Quartus auf "Kompilierung starten", es sollte keine Fehlermeldung generiert werden.

Wenn Sie eine Fehlermeldung über mehrere Pins erhalten. Gehen Sie zu Zuweisungen -> Gerät -> Geräte- und Pinoptionen -> Dual-Purpose-Pins -> ändern Sie den Wert des entsprechenden Pins auf "Als reguläre E/A verwenden".

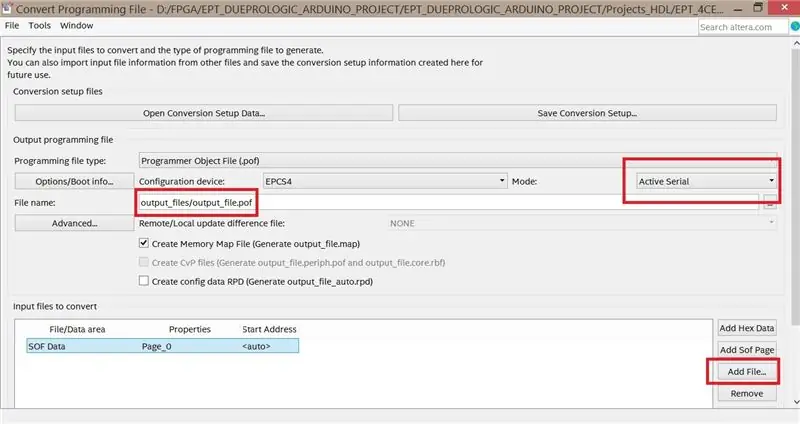

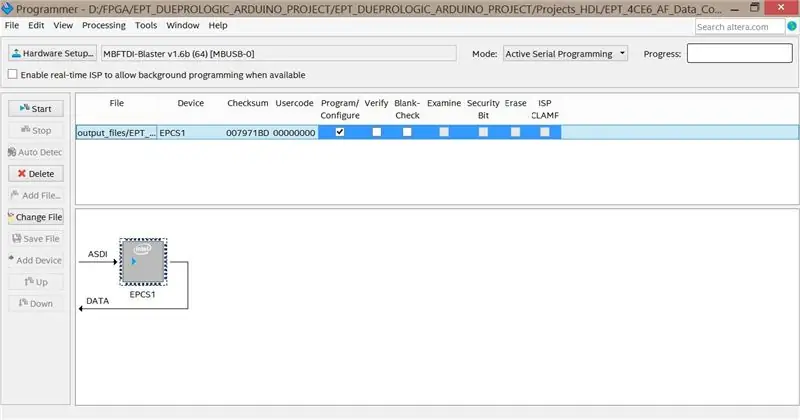

Nach der Kompilierung sollten Sie die pof-Ausgabedatei direkt erhalten. Wenn Ihre Software nicht auf dem neuesten Stand ist, erhalten Sie möglicherweise nur die sof-Datei. Wenn es passiert, klicken Sie in Quartus auf "Datei" -> "Programmdateien konvertieren". Ändern Sie die Einstellungen, die durch rote Kästchen gekennzeichnet sind.

Schritt 5: Versuchen wir es

Schließlich sollte es funktionieren!!! Die gelbe LED leuchtet immer. Die rote LED blinkt. Die blaue LED wird ausgeschaltet, wenn Sie die Taste B drücken. Die grüne LED wird eingeschaltet, wenn Sie die Taste A drücken

Empfohlen:

Temperatur CubeSat Ben & Kaiti & Q Stunde 1: 8 Schritte

Temperatur-CubeSat Ben & Kaiti & Q Stunde 1: Wollten Sie schon immer etwas selbst herstellen, das ins All geschickt werden kann und die Temperatur eines anderen Planeten misst? In unserem Physikunterricht an der High School wurden wir beauftragt, einen CubeSat mit einem funktionierenden Arduino mit der Hauptfrage zu bauen, wie können wir

COVID-19-Dashboard (einfach & leicht): 4 Schritte

COVID-19-Dashboard (einfach & leicht): Überall gibt es einen riesigen Ausbruch des neuartigen COVID-19-Virus. Es wurde notwendig, das aktuelle Szenario von COVID-19 im Land im Auge zu behalten. Zu Hause dachte ich an folgendes Projekt: "Ein Informations-Dashboard" - Ein Da

‘Runde’ Word Clock (auf Niederländisch & Englisch!): 8 Schritte (mit Bildern)

‘Runde’ Word Clock (auf Niederländisch & Englisch!): Vor einigen Jahren habe ich zum ersten Mal eine Word Clock im Internet gesehen. Seitdem wollte ich immer selbst einen machen. Es gibt viele Instructables, aber ich wollte etwas Originelles machen. Ich weiß nicht viel über Elektronik, also habe ich ein

6502 & 6522 Minimal Computer (mit Arduino MEGA) Teil 2: 4 Schritte

6502 & 6522 Minimal Computer (mit Arduino MEGA) Teil 2: Nach meinem vorherigen Instructable habe ich jetzt den 6502 auf eine Streifenplatine gelegt und einen 6522 Versatile Interface Adapter (VIA) hinzugefügt. Auch hier verwende ich eine WDC-Version des 6522, da sie perfekt zu ihrem 6502 passt. Diese neuen c

$3 & 3 Steps Laptopständer (mit Lesebrille & Stiftablage): 5 Schritte

3 $ & 3 Steps Laptopständer (mit Lesebrille & Stiftablage): Dieser $ 3 & Der Laptopständer mit 3 Schritten kann innerhalb von 5 Minuten hergestellt werden. Es ist sehr stark, leicht und kann zusammengeklappt werden, um es überall hin mitzunehmen