Inhaltsverzeichnis:

- Schritt 1: Erstellen einer PWM-Modul-Quelldatei

- Schritt 2: Aufbau eines PWM-Moduls - Vivado Setup

- Schritt 3: Erstellen eines PWM-Moduls - Erstellen Sie eine Projektdatei

- Schritt 4: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (I)

- Schritt 5: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (II)

- Schritt 6: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (III)

- Schritt 7: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (IV)

- Schritt 8: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (V)

- Schritt 9: Aufbau eines PWM-Moduls - Hardwareinstallation

- Schritt 10: Erstellen eines PWM-Moduls - Generieren Sie Bitstream und starten Sie das SDK

- Schritt 11: Erstellen eines PWM-Moduls - Erstellen Sie eine neue Anwendung im Xilinx SDK

- Schritt 12: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (I)

- Schritt 13: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (II)

- Schritt 14: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (III)

- Schritt 15: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (I)

- Schritt 16: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (II)

- Schritt 17: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (III)

- Schritt 18: Erstellen eines PWM-Moduls - Machen Sie es zum Laufen

- Schritt 19: Streaming-Videoverarbeitung auf Digilent ZYBO mit OV7670

- Schritt 20: Blockschaltbild vervollständigen

- Schritt 21: Verbinden Sie den OV7670 mit dem ZYBO

- Schritt 22: Blockdesign erstellen

- Schritt 23: VHDL-Dateien für die OV7670-Kamerasteuerung und -Aufnahme hinzufügen

- Schritt 24: Einschränkungsdatei hinzufügen

- Schritt 25: IP-Repo für HLS IP hinzufügen

- Schritt 26: Module und IP hinzufügen

- Schritt 27: IP-Konfigurationseinstellungen

- Schritt 28: PS-IP-Block hinzufügen und konfigurieren

- Schritt 29: Teil 1. Aufbau eines PWM-Moduls für Servomotoren

- Schritt 30: Anschlüsse der Videoeingangsseite (aclk hervorgehoben)

- Schritt 31: Verbindungen zu OV7670

- Schritt 32: Anschlüsse auf der Videoausgangsseite

- Schritt 33: Block- und Verbindungsautomatisierung ausführen

- Schritt 34: HDL-Wrapper generieren

- Schritt 35: Bitstream generieren, Hardware in SDK exportieren, SDK von Vivado starten

- Schritt 36: SDK (kein FreeRTOS)

- Schritt 37: FreeRTOS-Implementierung

- Schritt 38: Gebrauchsanweisung

- Schritt 39: Referenzen und Links

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:21.

- Zuletzt bearbeitet 2025-06-01 06:08.

Beginnen Sie mit Schritt eins, um Details zum Erstellen eines 2-Achsen-Servo-PWM-Controllers zu erhalten.

Beginnen Sie mit dem massiven Blockdiagramm (Schritt 19) für das vollständige Projekt.

Kamera + Schwenk-/Neige-Setup, das wir verwendet haben:

Zum Anschluss der Servos wurde der PmodCON3 von Digilent verwendet.

Schritt 1: Erstellen einer PWM-Modul-Quelldatei

Schritt 2: Aufbau eines PWM-Moduls - Vivado Setup

Laden Sie zunächst die Vivado Design Suite von der Xilinx-Website herunter. Installieren Sie die gesamte Design-Suite, einschließlich des Vivado Software Development Kit (SDK). Dieses Projekt verwendet die Version 2017.2.

In der Zwischenzeit soll Digilent Adept 2 auch als Zybo-Board-Treiber installiert werden.

Schritt 3: Erstellen eines PWM-Moduls - Erstellen Sie eine Projektdatei

Bevor Sie eine Projektdatei erstellen, sollten Sie sicherstellen, dass Sie die Zybo-Datei bereits ordnungsgemäß als Tutorial hier installiert haben:

Vivado Version 2015.1 und höher Installation der Board-Datei

Öffnen Sie Vivado 2017.2. Klicken Sie im Schnellstart auf Projekt erstellen -> Weiter -> Projektname (Nennen Sie hier Ihren Projektnamen) -> Projekttyp. Wählen Sie als Projekttyp RTL-Projekt aus und markieren Sie „Zu diesem Zeitpunkt keine Quellen angeben“. Als nächstes wählen Sie für den Standardteil „Boards“und „Zybo“als Anzeigename. Klicken Sie anschließend auf Fertig stellen, um das Projekt zu starten.

Schritt 4: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (I)

Klicken Sie im Flow Navigator auf „Blockdesign erstellen“und drücken Sie dann OK. Klicken Sie auf das „+“-Zeichen, um die erforderlichen IPs hinzuzufügen. Hinzufügen:

- Ein ZYNQ7-Verarbeitungssystem Zwei AXI-Timer

- Zwei AXI-Timer

Schritt 5: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (II)

Führen Sie nach dem Hinzufügen von IPs die Blockautomatisierung und die Verbindungsautomatisierung aus. Sobald die Automatisierung abgeschlossen ist, klicken Sie im Block „axi_timer_0“mit der rechten Maustaste auf pwm0 -> Make External. Benennen Sie den externen Pin pwm0 als pwm_Xaxis. Wiederholen Sie auch den obigen Vorgang am Block „axi_timer_1“und benennen Sie den externen Pin pwm0 als pwm_Zaxis.

Schritt 6: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (III)

Beachten Sie, dass wir jedes Mal, wenn wir das Blockdesign in Vivado beenden, einen HDL-Wrapper erstellen müssen. Da es das oberste Modul für jedes Projekt sein wird.

Schritt 7: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (IV)

Jetzt müssen wir unsere Einschränkungsdatei einrichten, um Pins zuzuweisen, die mit unserem Blockdiagramm verbunden sind. Schließen Sie das Blockdesign-Fenster, auf der Registerkarte "Quellen", "Quellen hinzufügen"->Einschränkungen hinzufügen oder erstellen-> fügen Sie die Zybo-Master.xdc als unsere Einschränkungsdateien hinzu.

Schritt 8: Erstellen eines PWM-Moduls - Blockdesign und Einstellung der Einschränkungsdatei (V)

Öffnen Sie die Einschränkungsdatei Zybo-Master.xdc aus dem Ordner "Constraints", entkommentieren Sie die Ports, die wir als Ausgangssignale angeben möchten, und benennen Sie " get_ports{XXXX}" um, wobei XXXX den im Blockdiagramm genannten externen Pin bezeichnet. Die Einstellung der Einschränkungsdatei ist in der Abbildung dargestellt.

Schritt 9: Aufbau eines PWM-Moduls - Hardwareinstallation

Verbinden Sie die Servomotoren mit dem Pmod CON3. TowerPro SG90 ist das Servomotormodell, das wir in diesem Projekt verwendet haben. Bei den Servomotorkabeln stellt das orange Kabel das PWM-Signal dar, das mit dem SIG-Pin in Pmod CON3 verbunden ist. Das rote Kabel Vcc ist ein Stromkabel, das mit dem VS-Pin in Pmod CON3 verbunden ist. Schließlich ist der braune Draht Gnd ein Massedraht, der mit dem GND-Pin verbunden ist. Als nächstes fügen Sie den Pmod CON3 in die obere Reihe des JD-Ports im Zybo-Board ein.

Schritt 10: Erstellen eines PWM-Moduls - Generieren Sie Bitstream und starten Sie das SDK

1. Führen Sie auf der Registerkarte Projektnavigator die Option BitStream generieren aus.

2. Hardware exportieren: Datei > Exportieren > Hardware exportieren -> Markierung auf „Bitstream einschließen“-> OK 3. SDK starten: Datei -> SDK starten.

Schritt 11: Erstellen eines PWM-Moduls - Erstellen Sie eine neue Anwendung im Xilinx SDK

Erstellen Sie eine neue Anwendung:

Datei > Neu > Anwendungsprojekt -> Geben Sie den Namen Ihres Projekts ein -> Fertig stellen

Unter Projekt-Explorer sollten sich drei Ordner befinden.

In diesem Fall ist „design_1_wrapper_hw_platform_0“der zuvor von Vivado exportierte Ordner. Axis_2_PWM_SDK_bsp ist der Ordner für das Board Support Package. Und Axis_2_PWM_SDK ist unser Hauptprojektordner im SDK. Sie können die Datei „helloworld.c“im Ordner „src“von Axis_2_PWM_SDK sehen, wobei „helloworld.c“die Hauptdatei ist.

Schritt 12: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (I)

Lassen Sie uns einige Dateien im Projekt-Explorer überprüfen. Öffnen Sie zunächst im Ordner „design_1_wrapper_hw_platform_0“die „system.hdf“. Diese Datei zeigt die Adresszuordnung für den Prozessor ps7_cortex9 und die in unserem Design vorhandenen IP-Blöcke.

Schritt 13: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (II)

Überprüfen Sie dann die Dateien „include“und „libsrc“im Ordner „Axis_2_PWM_SDK_bsp“. Bibliotheksdateien hier ermöglichen es uns, mit Hardware-Peripheriegeräten zu interagieren, ohne Register zu „spielen“.

Schritt 14: Erstellen eines PWM-Moduls - Überblick über den Projekt-Explorer (III)

In der BSP-Dokumentation wird xtmrctr.h als Xilinx Timer Control Library für AXI Timer gefunden. Typischerweise könnten wir hier die gewünschte PWM-Funktion finden. Liest man jedoch die Dokumentation „tmrctr_v4_3“, zeigt sich, dass der Treiber den PWM-Betrieb des Gerätes derzeit nicht unterstützt. Aufgrund des Mangels an PWM-Funktion müssen wir unsere PWM-Funktion mit Hilfe von xtmrctr.h und AXI Timer v2.0 LogiCORE IP Product Guide abschließen.

Schritt 15: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (I)

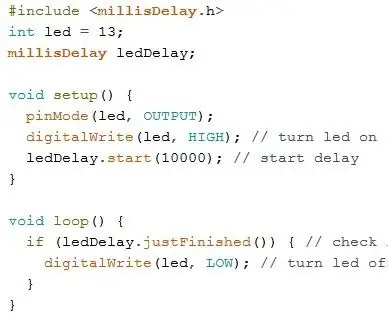

Zurück zur Hauptdatei „helloworld.c“, fügen Sie die folgenden Header-Dateien ein:

Schritt 16: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (II)

Definieren Sie die Basisadressen von zwei AXI TImern über „xparameters.h“.

Schritt 17: Aufbau eines PWM-Moduls - Wrap-Up-PWM-Funktion (III)

Erstellen Sie die gewünschte PWM-Funktion.

Duty_val: wandelt den Gradwert in das Tastverhältnis um. PWM_Freq_Duty: Stellen Sie die gewünschte Frequenz und das Tastverhältnis ein, um PWM zu erzeugen. Taktperiode sollte auch zugewiesen werden.

PWM_START: Weisen Sie die PWM-Registeradresse zu und starten Sie die PWM-Generierung.

PWM_STOP: Weisen Sie die PWM-Registeradresse zu und beenden Sie die PWM-Generierung.

Der restliche Democode wird in „helloworld.c“unter „Axis_2_PWM_SDK“angezeigt.

Schritt 18: Erstellen eines PWM-Moduls - Machen Sie es zum Laufen

1. Programmieren Sie das FPGA über das SDK

- Verbinden Sie das Zybo Board über den USB-Port mit dem PC.

- Xilinx Tools -> FPGA programmieren

2. Führen Sie das Programm aus

Klicken Sie auf das Symbol "Ausführen" und öffnen Sie das Menü -> Ausführen als -> Auf Hardware starten

3. SDK-Terminal

- Öffnen Sie das SDK-Terminal -> Mit seriellem Port verbinden -> OK

- Führen Sie das Programm aus. Wenn der Democode erfolgreich ausgeführt wird, sollten Sie "Initialisierung abgeschlossen!" sehen. auf dem SDK-Terminal.

Schritt 19: Streaming-Videoverarbeitung auf Digilent ZYBO mit OV7670

Vollständige Archivdatei angehängt.

Schritt 20: Blockschaltbild vervollständigen

Dies zeigt das vollständige Diagramm aller Verbindungen und IP-Blöcke im Projekt

Schritt 21: Verbinden Sie den OV7670 mit dem ZYBO

Stellen Sie eine Verbindung her, um das ov7670-Modul mit den ZYBO Pmods zu verbinden

Daten Pmod ist Pmod D

Kontroll-Pmod ist Pmod C

Verbinden Sie außerdem den PmodCON3 und die Servos wie in der ersten Hälfte dieses Tutorials beschrieben

Schritt 22: Blockdesign erstellen

Klicken Sie in Flow Navigator auf „Blockdesign erstellen“und drücken Sie dann OK.

Schritt 23: VHDL-Dateien für die OV7670-Kamerasteuerung und -Aufnahme hinzufügen

Fügen Sie die an diesen Schritt angehängten VHDL-Dateien zum Projekt hinzu

Schritt 24: Einschränkungsdatei hinzufügen

Fügen Sie die angehängte Einschränkungsdatei zu Ihrem Projekt hinzu.

Schritt 25: IP-Repo für HLS IP hinzufügen

Nehmen Sie die angehängte Zip-Datei und entpacken Sie sie in einen neuen Ordner mit ähnlichem Namen in einem neuen Verzeichnis (Ordner) namens "HLS_repo".

Fügen Sie Ihrem Projekt ein IP-Repository hinzu, indem Sie zum IP-Katalog gehen und mit der rechten Maustaste auf "Repository hinzufügen…" klicken.

Navigieren Sie zu Ihrem Verzeichnis "HLS_repo" und wählen Sie es aus.

Optional: Erstellen Sie selbst den HLS-Videoverarbeitungsblock!

Schritt 26: Module und IP hinzufügen

Fügen Sie die Module ov7670_axi_stream_capture, debounce und ov7670_controller zum Blockdiagramm hinzu, indem Sie mit der rechten Maustaste auf den Hintergrund klicken und "Modul hinzufügen…" auswählen.

Fügen Sie auf ähnliche Weise die IPs hinzu:

- HLS_Video_Track

- Video-Frame-Puffer schreiben

- Video-Frame-Puffer lesen

- Video-Timing-Controller

- AXI4-Stream zum Videoausgang

- 3 von "Scheibe"

- Konstante

- 2 von AXI-Timer

Schritt 27: IP-Konfigurationseinstellungen

Wie in Bildern gezeigt

Schritt 28: PS-IP-Block hinzufügen und konfigurieren

Fügen Sie das ZYNQ7-Verarbeitungssystem zum Blockdiagramm hinzu

Bearbeiten Sie die Konfiguration:

-

PS-PL-Konfiguration

-

PS

- SHP aktivieren 0

- Aktivieren Sie SHP 1

-

-

Uhr-Konfiguration

-

PL Stoffuhren

- FCLK_0 bei 100MHz

- FCLK_1 bei 25MHz (OutputClock)

- FLCK_2 bei 35MHz (<=50MHz) (CameraClock)

-

Schritt 29: Teil 1. Aufbau eines PWM-Moduls für Servomotoren

Bringen Sie axi_timer_0 pwm0 zum neuen Ausgangsport pwm_Xaxis

Bringen Sie axi_timer_1 pwm0 zum neuen Ausgabeport pwm_Zaxis

Schritt 30: Anschlüsse der Videoeingangsseite (aclk hervorgehoben)

Schließen Sie die IP-Blöcke der Videoeingangsseite richtig an

(* diese Verbindungen sollten durch Auswahl der richtigen Optionen während der Verbindungsautomatisierung erstellt werden) "aclk" aus axi_stream_capture geht an:

- ap_clk beim Schreiben des Video-Frame-Puffers

- ap_clk auf HLS-Videostream-Verarbeitungsblock

- *aclk auf AXI smartconnect IP vom Video Frame Buffer Write to the S_AXI_HP0

- *aclk entsprechend den Kanälen der AXI Interconnect IP für die S_AXI Kanäle des HLS Video Processing Blocks und des Video Frame Buffer schreiben S_AXI_HP0_ACLK auf den PS Block

Das Videostream-Signal wird einfach vom Aufnahmeblock in Reihe zum Zynq-Speicherinterface geschaltet.

- Video geht vom Aufnahmeblock zum HLS-Verarbeitungsblock.

- Das verarbeitete Video vom HLS-Block geht an den Bildpuffer-Schreibblock.

- *Der Framebuffer-Schreibblock verbindet sich mit der HP0-Schnittstelle des Zynq PS-Blocks.

- Das m_axis_tuser-Signal vom Ausgang des Capture-Blocks wird manuell sowohl mit dem video_in_TUSER-Eingangssignal am HLS-Verarbeitungsblock als auch mit dem ap_start-Signal am selben Block verdrahtet.

Das Signal TUSER(tuser) wird vom AXI-Videostream-Protokoll verwendet, um den Beginn eines Frames des Videos anzuzeigen. AP_Start weist den HLS-Block an, mit der Verarbeitung zu beginnen an. Wenn Sie ein einzelnes Signal eines Busses anschließen und auf diese Weise abtrennen, müssen Sie es auch am normalen Abschlusspunkt des restlichen Busses anschließen. Vivado geht davon aus, dass Sie, wenn Sie das Signal manuell verbinden, die Verbindung trennen möchten, mit der es normalerweise verbunden wäre.

Konfigurationseinstellungen von IP-Blöcken:

Video-Frame-Puffer schreiben:

Videoformate: RGB8

1 Sample pro Takt Max. Spalten: 1280 (>=640) Max. Zeilen: 960 (>=480) Max. Datenbreite: 8

Schritt 31: Verbindungen zu OV7670

Auf dem ov7670_axi_stream_capture-Block

- Machen Sie alle Eingänge extern (klicken Sie mit der rechten Maustaste auf einen Pin und wählen Sie aus dem Menü oder klicken Sie mit der linken Maustaste -> Strg + T)

- Lass die Namen wie sie sind

Auf dem ov7670_controller-Block

- Machen Sie alle Blockausgänge extern

- Benennen Sie den Port config_finished in led0 um

- clk mit CameraClock verbinden (<=50MHz) (FCLK_2)

Auf dem Entprellblock

- Verbinden Sie den Eingang von button1 mit einem externen Eingang namens btn0

- Verbinden Sie out1 mit der Resend-Leitung am IP-Block ov7670_controller

- Verbinden Sie den Button2-Eingang mit einem externen Eingangsanschluss namens btn3

- Verbinden Sie out2n mit dem Eingang ext_reset_in der Prozessorsystem-Reset-IP für die Videoaufnahme-Taktdomäne. (*Dies muss möglicherweise erfolgen, nachdem die IP generiert wurde*)

- clk mit CameraClock verbinden (<=50MHz) (FCLK_2)

Schritt 32: Anschlüsse auf der Videoausgangsseite

Anschlüsse für Blöcke Video Timing Controller (VTC), AXI4-Stream to Video Out und Slices

- Verwenden Sie 25 MHz Takt (FCLK_1) für vid_io_out_clk und VTC clk

- Verwenden Sie den 100-MHz-Takt (FCLK_0) für die Eingabe von AXI4-Stream zum Videoausgang

- vtiming_out nach vtiming_in

- Video Frame Buffer Read m_axis_video geht an AXI4-Stream an Video Out video_in

- vtg_ce geht zu gen_clken

- Binden Sie VTC clken, aclken, vid_io_out_ce an Constant dout[0:0]

- Bringen Sie vid_hsync und vid_vsync an die externen Ausgabeports vga_hs bzw. vga_vs. (nicht abgebildet)

Scheiben:

-

Slices sollten wie in den beigefügten Bildern gezeigt eingerichtet werden

- Benennen Sie die Blöcke in Slice_red, Slice_Green und Slice_Blue um

- Richten Sie die Slice-Bereiche wie in den Bildern gezeigt gemäß dem Namen des Blocks ein

- Verbinden Sie jeden Slice-Ausgang mit einem externen Port-Ausgang, wie in der Abbildung gezeigt.

- vid_data[23:0] verbindet sich mit den Eingängen für jedes Slice (Din[23:0])

Schritt 33: Block- und Verbindungsautomatisierung ausführen

Führen Sie die Blockautomatisierung aus, um die Dinge aus dem ZYNQ7 PS-Block zu verbinden. Wie auf dem Bild gezeigt.

Führen Sie die Verbindungsautomatisierung aus, um alle Verbindungs-IPs zu erstellen. Achten Sie genau auf alle Optionen in jedem Bild.

Verbinden Sie im Entprellblock out2n mit dem Eingang der Videoaufnahmetaktdomäne Processor System Reset ext_reset_in.

Schritt 34: HDL-Wrapper generieren

Generieren Sie den HDL-Wrapper für Ihr Blockdesign.

Legen Sie es als oberstes Modul fest.

Schritt 35: Bitstream generieren, Hardware in SDK exportieren, SDK von Vivado starten

Stellen Sie sicher, dass Sie Bitstream in den Export einbeziehen.

Die Generierung des Bitstroms kann sehr lange dauern.

Dann SDK starten

Schritt 36: SDK (kein FreeRTOS)

Diese Version macht alles, ohne FreeRTOS zu verwenden, und komprimiert den Code gut.

Erstellen Sie ein eigenständiges BSP basierend auf dem Hardwaredesign. Die Standardoptionen sollten in Ordnung sein. Stellen Sie sicher, dass BSP-Quellen generiert wurden.

Erstellen Sie die App wie im Bild gezeigt. (leerer Antrag)

Löschen Sie die automatisch generierte Hauptdatei und importieren Sie die angehängten Dateien.

Schritt 37: FreeRTOS-Implementierung

Diese Version verwendet FreeRTOS. Erstellen Sie ein FreeRTOS901-BSP basierend auf dem Hardware-Design. Die Standardoptionen sollten in Ordnung sein. Stellen Sie sicher, dass BSP-Quellen generiert wurden.

Erstellen Sie die App wie im Bild gezeigt. (leerer Antrag)

Löschen Sie die automatisch generierte Hauptdatei und importieren Sie die angehängten Dateien.

Schritt 38: Gebrauchsanweisung

Dieses Projekt ist ein bisschen schwierig zu starten. Befolgen Sie die Schritte der Reihe nach.

Stellen Sie sicher, dass Ihr ZYBO beim Einschalten nichts selbst lädt. Das bedeutet, dass die Done-LED nicht aufleuchten sollte. Eine Möglichkeit, dies zu tun, besteht darin, den Boot-Source-Jumper auf JTAG zu setzen.

Öffnen Sie das Projekt (FreeRTOS oder nicht), das Sie aus dem SDK programmieren möchten

- Schalten Sie Ihren ZYBO ein. Die Done-LED sollte nicht aufleuchten.

- Programmieren Sie das FPGA mit der Bitdatei. Die Done-LED sollte aufleuchten. Led0 sollte nicht leuchten.

- Führen Sie den Code aus (denken Sie daran, den Starthaltepunkt zu überschreiten, wenn Sie dies tun).

An diesem Punkt sollten Sie eine Ausgabe auf Ihrem VGA-Display erhalten.

Um neu zu starten (falls es einen Fehler gibt oder was auch immer): Tippen Sie schnell auf die PS-SRST-Taste oder schalten Sie den ZYBO aus und wieder ein. Fahren Sie ab Schritt 2 fort.

Wenn Sie den Prozessor mit dem Debugger anhalten, hält die Kamera die Position, anstatt sich zu bewegen. Der Videostream wird trotzdem fortgesetzt.

Schritt 39: Referenzen und Links

Xilinx-Referenzhandbücher und -Dokumentation:

- PG044 - AXI-Stream zum Videoausgang

- PG278 - Lesen/Schreiben des Video-Frame-Puffers

Andere Links:

- Lauris Blog - VDMA-Input

- Lauris Blog - OV7670 zu VGA-Ausgabe mit BRAM

- Hamsterworks-Wiki von Mike Fields, die Originalquelle des OV7670-Codes

- Datenblatt mit grundlegenden Timing-Spezifikationen

Empfohlen:

Heimwerken -- Einen Spinnenroboter herstellen, der mit einem Smartphone mit Arduino Uno gesteuert werden kann – wikiHow

Heimwerken || Wie man einen Spider-Roboter herstellt, der mit einem Smartphone mit Arduino Uno gesteuert werden kann: Während man einen Spider-Roboter baut, kann man so viele Dinge über Robotik lernen. Wie die Herstellung von Robotern ist sowohl unterhaltsam als auch herausfordernd. In diesem Video zeigen wir Ihnen, wie Sie einen Spider-Roboter bauen, den wir mit unserem Smartphone (Androi

Bewegungsaktivierte Cosplay Wings mit Circuit Playground Express - Teil 1: 7 Schritte (mit Bildern)

Bewegungsaktivierte Cosplay-Flügel mit Circuit Playground Express - Teil 1: Dies ist Teil 1 eines zweiteiligen Projekts, in dem ich Ihnen meinen Prozess zur Herstellung eines Paars automatisierter Feenflügel zeige. Der erste Teil des Projekts ist der Mechanik der Flügel, und der zweite Teil macht es tragbar und fügt die Flügel hinzu

Raspberry Pi mit Node.js mit der Cloud verbinden – wikiHow

So verbinden Sie Raspberry Pi mit Node.js mit der Cloud: Dieses Tutorial ist nützlich für alle, die einen Raspberry Pi mit Node.js mit der Cloud, insbesondere mit der AskSensors IoT-Plattform, verbinden möchten. Sie haben keinen Raspberry Pi? Wenn Sie derzeit keinen Raspberry Pi besitzen, empfehle ich Ihnen, sich einen Raspberry Pi zuzulegen

DIY Circuit Activity Board mit Büroklammern - HERSTELLER - STEM: 3 Schritte (mit Bildern)

DIY Circuit Activity Board mit Büroklammern | HERSTELLER | STEM: Mit diesem Projekt können Sie den Weg des elektrischen Stroms ändern, um durch verschiedene Sensoren zu laufen. Mit diesem Design können Sie zwischen dem Aufleuchten einer blauen LED oder dem Aktivieren eines Summers wechseln. Sie haben auch die Wahl, einen lichtabhängigen Widerstand mit

Beginnen Sie mit Light Painting (kein Photoshop): 5 Schritte (mit Bildern)

Beginnend mit Light Painting (kein Photoshop): Ich habe vor kurzem eine neue Kamera gekauft und einige ihrer Funktionen untersucht, als ich im Internet auf Light Painting oder Langzeitbelichtung gestoßen bin. Die meisten von uns werden die Grundform des Lightpaintings mit einem Foto in einer Stadt mit einer Straße gesehen haben