Inhaltsverzeichnis:

- Schritt 1: Quellen hinzufügen und „Simulationsquellen hinzufügen oder erstellen“auswählen

- Schritt 2: Erstellen Sie eine Datei namens Enable_sr_tb

- Schritt 3: Testbench-Datei erstellen

- Schritt 4: Setzen Sie Enable_sr_tb als oberste Ebene unter der Simulation

- Schritt 5: Ausführen von Synthese und Verhaltenssimulation

- Schritt 6: Bewerten Sie das Simulationsergebnis

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:20.

- Zuletzt bearbeitet 2025-01-23 12:52.

Ich habe dieses Simulationsprojekt für eine Online-Klasse gemacht. Das Projekt wird von Verilog geschrieben. Wir werden die Simulation in Vivado verwenden, um die Wellenform in enable_sr(enable digit) aus dem zuvor erstellten Stoppuhrprojekt zu visualisieren. Darüber hinaus werden wir die Systemaufgabe nutzen, um von uns gemachte Fehler im Design anzuzeigen.

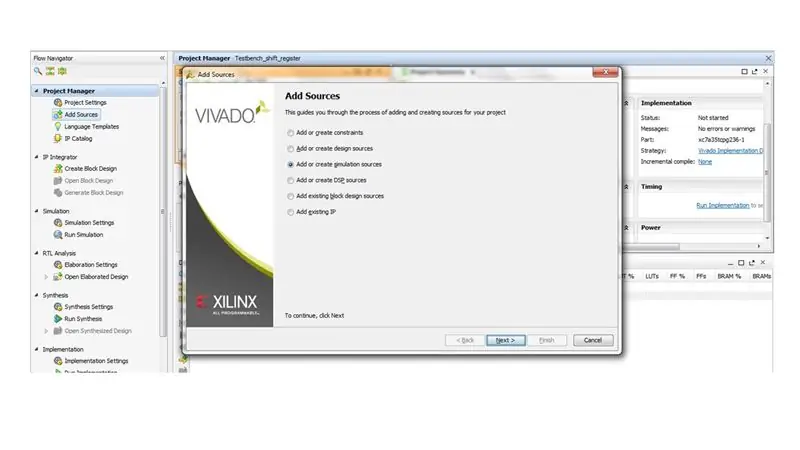

Schritt 1: Quellen hinzufügen und „Simulationsquellen hinzufügen oder erstellen“auswählen

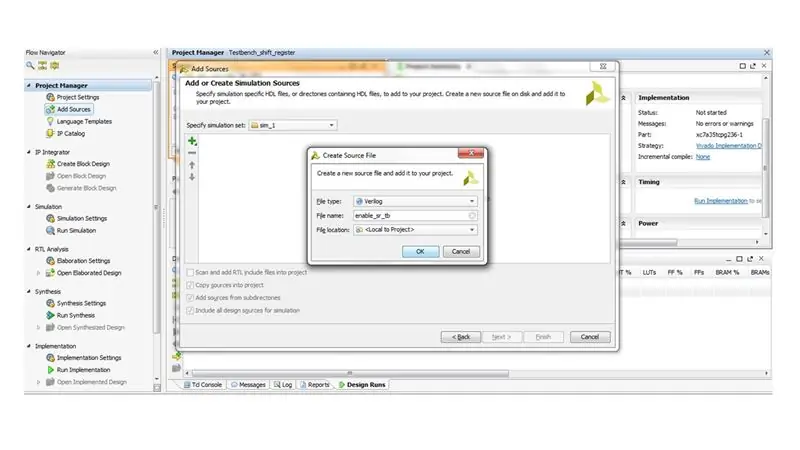

Schritt 2: Erstellen Sie eine Datei namens Enable_sr_tb

Schritt 3: Testbench-Datei erstellen

1. Importieren Sie das Modul enable_sr aus dem Stoppuhrprojekt. Das ist die Datei, die wir simulieren wollen

2. Erstellen Sie das Testbench-Modul enable_sr_tb();

3. Geben Sie Ein- und Ausgänge des Moduls enable_sr() ein. Denken Sie daran, dass die Eingänge für enable_sr jetzt im Registertyp sind, während die Ausgänge zum Netztyp werden.

4. Instanziieren Sie die zu testende Einheit (uut), die enable_sr. ist

5. Takt erzeugen, dessen Periode (T) 20 ns beträgt

6. Verwenden Sie die bedingte Anweisung, um ein Fehlerprüfsystem zu erstellen. In diesem Beispiel wollen wir prüfen, ob mehr als eine Ziffer aktiv ist.

Hinweis: In der ursprünglichen Datei enable_sr() sollten wir das Muster mit 4’b0011 initialisieren, damit zwei Ziffern aktiv sind, um einen Fehler zu erzeugen

7. Verwenden Sie die Systemaufgabe $display, um den Fehler anzuzeigen

8. Verwenden Sie die Systemaufgabe $finish, um die Simulation zum Zeitpunkt 400 ns. abzuschließen

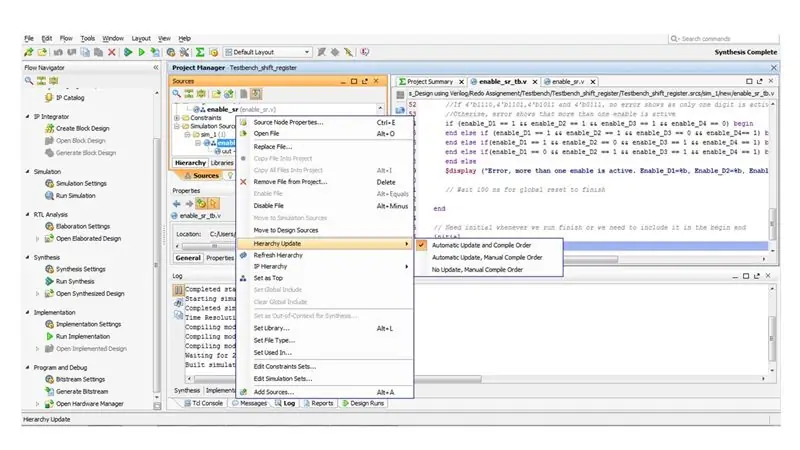

Schritt 4: Setzen Sie Enable_sr_tb als oberste Ebene unter der Simulation

Schritt 5: Ausführen von Synthese und Verhaltenssimulation

- Führen Sie vor dem Ausführen der Verhaltenssimulation die Synthese aus, um sicherzustellen, dass keine Syntaxfehler in der Testbench-Datei und der Einheit unter der Testdatei vorhanden sind

- Führen Sie die Verhaltenssimulation aus

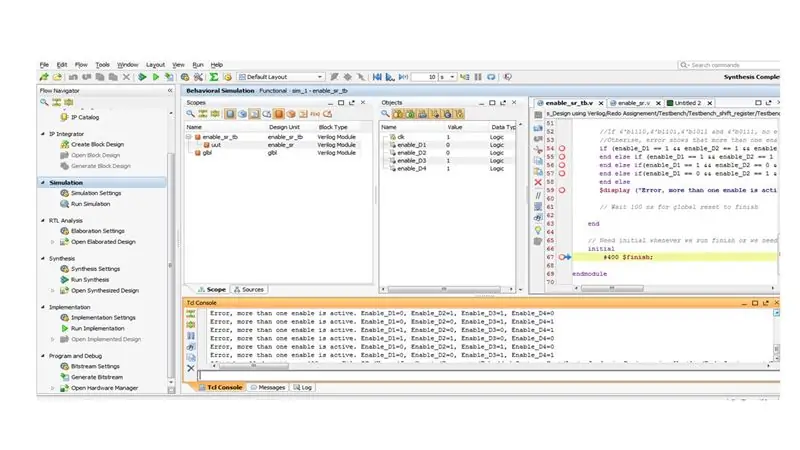

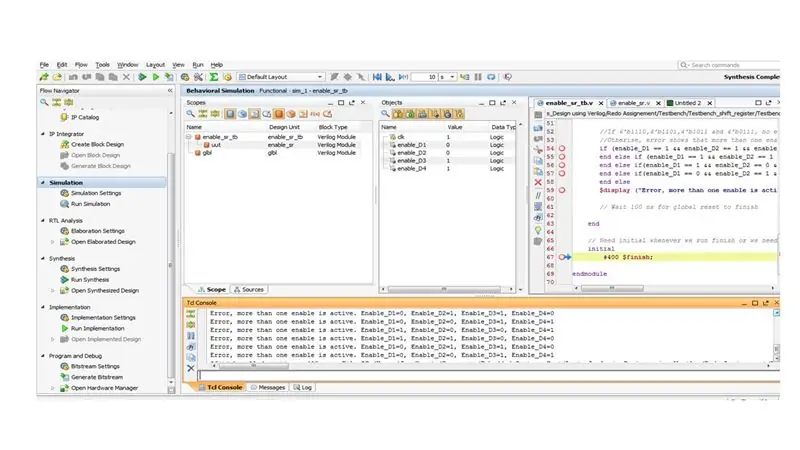

Schritt 6: Bewerten Sie das Simulationsergebnis

Sie sehen die Simulationsfenster. Es enthält verschiedene Panels.

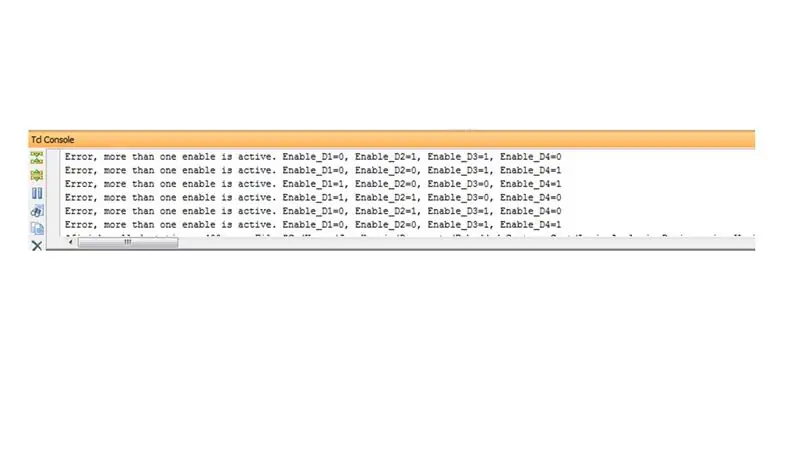

Die Fehlermeldung wird im Konsolenfenster angezeigt. Dies zeigt an, dass während des Simulationszeitraums mehr als eine Ziffer aktiv ist.

Sie können die Wellenform auch im Oszilloskop sehen

Anbei die Projektdatei.

Empfohlen:

So verwenden Sie Sensor21.com für die Sensorüberwachung: 3 Schritte

So verwenden Sie Sensor21.com für die Sensorüberwachung: Wenn Sie eine Plattform zur Überwachung und Steuerung entfernter Geräte und Sensoren für Ihre DIY-Projekte benötigen, ist sensor21.com möglicherweise eine gute Lösung für Sie. Es hat eine gebrauchsfertige benutzerfreundliche GUI. Einfach Sensoren hinzuzufügen und mit Grafiken zu überwachen. Stellen Sie Wecker für e

So verwenden Sie das Mac-Terminal und verwenden Sie die wichtigsten Funktionen - Gunook

So verwenden Sie das Mac-Terminal und verwenden Sie die wichtigsten Funktionen: Wir zeigen Ihnen, wie Sie das MAC-Terminal öffnen. Wir zeigen Ihnen auch einige Funktionen innerhalb des Terminals, wie ifconfig, Verzeichniswechsel, Zugriff auf Dateien und arp. Mit Ifconfig können Sie Ihre IP-Adresse und Ihre MAC-Anzeige überprüfen

So erhalten Sie Musik von fast jeder (Haha) Website (solange Sie sie hören können, können Sie sie bekommen Okay, wenn sie in Flash eingebettet ist, können Sie es möglicherweise nic

So erhalten Sie Musik von fast jeder (Haha) Website (solange Sie sie hören können, können Sie sie bekommen … Okay, wenn sie in Flash eingebettet ist, können Sie es möglicherweise nicht) BEARBEITET!!!!! Zusätzliche Informationen: Wenn Sie jemals auf eine Website gehen und ein Lied abspielen, das Sie mögen und es wollen, dann ist hier das anweisbare für Sie, nicht meine Schuld, wenn Sie etwas durcheinander bringen (nur so wird es passieren, wenn Sie ohne Grund anfangen, Dinge zu löschen) ) Ich konnte Musik für

Eine Media Center-Lösung, die sogar die Frau und die Kinder verwenden. - Gunook

Eine Media Center-Lösung, die sogar die Frau und die Kinder verwenden.: Dieses Instructable ist eine Zusammenfassung meiner Erfahrungen mit einer Vielzahl von Media Center-Apps, Betriebssystemen, Hardware und Dateiformaten. Dies ist keine PVR-Anleitung und erlaubt Ihnen nicht, Live-TV aufzunehmen oder zu pausieren, obwohl ich eine gute Alternative vorschlagen werde

Fügen Sie eine PC-Sync-Buchse zu einem Nikon Sc-28 Ttl-Kabel hinzu (verwenden Sie die automatischen Einstellungen für einen Blitz an der Kamera und lösen Sie Kamerablitze aus !!):

Fügen Sie eine PC-Sync-Buchse zu einem Nikon Sc-28 Ttl-Kabel hinzu (verwenden Sie die automatischen Einstellungen für einen Kamerablitz und lösen Sie die Kamerablitze aus !!): In dieser Anleitung zeige ich Ihnen, wie Sie einen dieser lästigen proprietären 3-Pin-TTL-Anschlüsse auf entfernen die Seite eines Nikon SC-28 Off-Camera-TTL-Kabels und ersetzen Sie es durch einen Standard-PC-Sync-Anschluss. Auf diese Weise können Sie einen dedizierten Blitz verwenden, s