Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:18.

- Zuletzt bearbeitet 2025-01-23 12:52.

In diesem anweisbaren werden wir einen SPI Bus Master von Grund auf in VHDL entwerfen.

Schritt 1: Überblick über SPI

- SPI ist ein synchroner serieller Bus

- Seine Popularität und Einfachheit machten es zu einem De-facto-Standard in der seriellen Kommunikation

- Vollduplex-Bus

- Einfaches Protokoll und einer der schnellsten seriellen Busse

Schritt 2: Designspezifikationen

Dies sind die Spezifikationen des SPI-Masters, den wir entwerfen werden:

- Unterstützt alle vier Betriebsmodi; dynamisch konfigurierbar

- Clock-Enable-Steuerung zum Energiesparen

- Statisch konfigurierbare Wortlänge und Geschwindigkeit

- Single Interrupt für Senden und Empfangen

Schritt 3: Starten

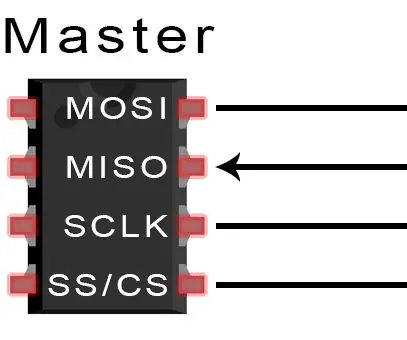

Zunächst sollte unsere IP zwei Schnittstellen haben. Eine ist eine serielle Schnittstelle und die andere ist eine parallele Schnittstelle. Die serielle Schnittstelle besteht aus den De-facto-Standardsignalen von SPI: MOSI, MISO, SS, SCLK.

MOSI wird manchmal als SDO und MISO manchmal als SDI bezeichnet.

Die serielle Schnittstelle wird verwendet, um mit externen Peripheriegeräten, dh SPI-Slaves, zu kommunizieren.

Die parallele Schnittstelle wird verwendet, um mit unserem Host zu kommunizieren, dh einem Mikrocontroller oder Mikroprozessor, der dem Master tatsächlich mitteilt, welche Daten seriell über die seriellen Leitungen übertragen und empfangen werden müssen. dh alle Datenbusse gehören zur parallelen Schnittstelle.

Wir haben eine globale Uhr, die die interne SPI-Logik steuert, sowie SCLK, die wir intern generieren.

Wir haben auch einige Steuersignale wie Schreibfreigabe, Taktfreigabe. Und Interrupt und andere Statussignale.

Da wir es mit komplexen Regelungsbedingungen zu tun haben, ist es einfacher, solche seriellen Kommunikations-IPs als FSM zu konzipieren. Wir werden den SPI-Master auch als FSM konzipieren. Die FSM wird von einem anderen internen Takt getrieben, der zweimal SCLK ist. Diese interne Uhr wird unter Verwendung von synchronen Zählern aus der globalen Uhr erzeugt.

Alle Steuersignale, die Taktdomänen überqueren, haben Synchronisierer, um auf der sicheren Seite zu sein.

Schritt 4: RTL-Ansicht des SPI-Master-Kerns und der Simulationswellenformen

Es handelt sich um ein reines RTL-Design, bei dem keine dedizierten FPGA-IPs verwendet werden. Daher ist es ein vollständig portierbarer Code für jedes FPGA.

Empfohlen:

Videospiel-Tutorial-Design: 6 Schritte

Videospiel-Tutorial-Design: Ich bin ein Hobby-Spieleentwickler, mit meinen Hauptinteressen im Spieledesign und der Programmierung. Um meine Fähigkeiten zu üben und aufzufrischen, mache ich ab und zu einfache Spiele, die ich mit meinen Freunden und Geschwistern teile. Früher würde ich dem Pla die Regeln erklären

So verwandeln Sie Ihr Design in eine professionelle Leiterplatte - Mein Ansatz: 9 Schritte

So verwandeln Sie Ihr Design in eine professionelle Leiterplatte | Mein Ansatz: In diesem Beitrag werde ich meinen Ansatz zum Bau einer professionellen Leiterplatte in sehr wenigen detaillierten Schritten teilen. Ich habe auch ein Video desselben eingebettet, Sie können es sich ansehen oder den Beitrag für die detaillierte Erklärung weiterlesen. Beginnen wir also mit der

Fehlerbehebung bei einem PCB-Design?: 8 Schritte (mit Bildern)

Wie behebe ich ein PCB-Design?: Jedes Mal, wenn ich eine PCB entwerfe, möchte ich meine Grenzen ein wenig überschreiten und etwas ausprobieren, was ich noch nie zuvor ausprobiert habe. Dieses Mal wollte ich die Möglichkeit hinzufügen, dieses Board ohne externen Programmierer zu programmieren. Ich habe einige billige USB-zu-UART-Konverter namens CH gefunden

GRUNDLAGEN DES SPI-KOMMUNIKATIONSPROTOKOLLS: 13 Schritte

GRUNDLAGEN DES SPI-KOMMUNIKATIONSPROTOKOLLS: Wenn Sie einen Mikrocontroller mit einem Sensor, Display oder einem anderen Modul verbinden, denken Sie dann jemals darüber nach, wie die beiden Geräte miteinander kommunizieren? Was genau sagen sie? Wie können sie sich verstehen?Kommunikation zwischen elektronischen Geräten

â-’.::*, Awesome Design (Microsoft Paint), *::.â-’: 4 Schritte

â-’.::*,Awesome Design (Microsoft Paint),*::.â-’: Ich zeige Ihnen, wie Sie mit Microsoft Paint oder einfach nur mit Bleistift und Papier ein tolles Design erstellen! ! PS Bitte bewerten und abstimmen für den Buchwettbewerb. Tausend Dank