Inhaltsverzeichnis:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 07:17.

- Zuletzt bearbeitet 2025-01-23 12:52.

Verbinden Sie Ihr Mojo-Entwicklungsboard mit diesem Shield mit externen Eingängen.

Was ist das Mojo-Entwicklungsboard?

Das Mojo-Entwicklungsboard ist ein Entwicklungsboard, das auf dem Spartan 3 FPGA von Xilinx basiert. Das Brett wird von Alchitry hergestellt. FPGAs sind sehr nützlich, wenn mehrere Prozesse gleichzeitig ausgeführt werden müssen.

Was werden Sie brauchen?

Lieferungen

Mojo-Entwicklungsboard

Gerber-Datei

8 x 15k Ohm Widerstände (optional*)

4 x 470 Ohm Widerstände

4 x 560 Ohm Widerstände

4 x CC Sieben-Segment-Anzeigen

4 x 3 mm LEDs

4 x SPDT-Tastschalter

1 x 4-Positionen-DIP-Schalter für die Oberflächenmontage

2 x 25 x 2 oder 4 x 25 Header

1x 2 x 5 Stiftkastenkopf

Lötkolben

Lot

Fluss

*(wenn diese Widerstände weggelassen werden, muss interner Pullup/Pulldown für die entsprechenden Pins aktiviert werden)

Schritt 1: Gerber zum Leiterplattenhersteller Ihrer Wahl hochladen

Für meine Boards habe ich bei JLC PCB bestellt.

Die einzige Änderung, die ich vorgenommen habe, war die Farbe, die ich dem Schwarz des Mojo anpassen wollte.

Schritt 2: Platinenmontage

Beim Löten finde ich es immer sinnvoll, die untersten Teile zuerst zu löten, daher ist es eine gute Idee, mit den Widerständen zu beginnen.

R5, R6, R7, R8, R9, R10, R11 und R12 sind 15k-Ohm-Widerstände, die zum Herunterziehen der Schalter verwendet werden (wenn Sie internen Pullup / Pulldown verwenden, ignorieren Sie dies).

R1, R2, R3, R4 sind 560-Ohm-Widerstände, die für die Begrenzung des Stroms durch die 7-Segment-Anzeige verantwortlich sind.

R13, R14, R15, R16 sind 470 Ohm Widerstände, die für die Begrenzung des Stroms durch die 4 LEDs verantwortlich sind.

Als nächstes löten Sie den Dip-Schalter, die taktilen Schalter, die LEDs, die Sieben-Segment-Anzeigen und den Box-Header-Anschluss in dieser Reihenfolge.

Platzieren Sie nun die 25 x 2 (oder 2 25 x 1) in das Mojo, um die Stifte auszurichten. Richten Sie die Abschirmung an den Stiften aus und löten Sie sie an.

Schritt 3: Software-Setup

Bei Software, die auf die Alchitry-Website verweist, erfahren Sie, was Sie für die ersten Schritte und die Installation der Xilinx ISE benötigen. Es ist jedoch wichtig, die.ucf-Datei zu ändern, damit sie weiß, welche Pins mit dem verbunden sind, was wichtig ist, um Ihr Programm zum Laufen zu bringen.

Hier ist die.ucf-Datei, die ich mit dem Schild verwende:

KONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODE "clk" 50 MHz HOCH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q[0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q[1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q[2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q[3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S[0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S[1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S[2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S[3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb[1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb[2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb[3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb[4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega[0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege[0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg[0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega[1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege[1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg[1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega[2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege[2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg[2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega[3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege[3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg[3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDARD = LVTTL;

Denken Sie daran, wenn Sie die Pulldown-Widerstände nicht installiert haben, um die Pins in der.ucf mit zu bearbeiten

| HERUNTERZIEHEN; Ö

| AUFZIEHEN;

Wenn Sie den Block für irgendetwas verwenden möchten, sind die Verbindungen wie folgt. Links ist die Block-Pin-Nummer und rechts ist die Mojo-Pin-Nummer, die Sie in Ihrer.ucf zuweisen sollten:

Stift 1 = 29

Stift 2 = 51

Stift 3 = 32

Stift 4 = 41

Stift 5 = 34

Stift 6 = 35

Stift 7 = 40

Stift 8 = 33

Pin 9 = GND

Stift 10 = +V

Empfohlen:

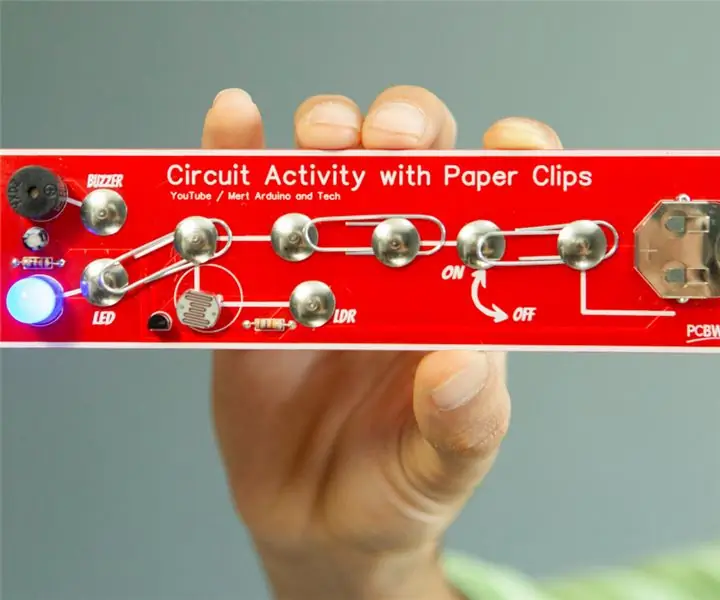

DIY Circuit Activity Board mit Büroklammern - HERSTELLER - STEM: 3 Schritte (mit Bildern)

DIY Circuit Activity Board mit Büroklammern | HERSTELLER | STEM: Mit diesem Projekt können Sie den Weg des elektrischen Stroms ändern, um durch verschiedene Sensoren zu laufen. Mit diesem Design können Sie zwischen dem Aufleuchten einer blauen LED oder dem Aktivieren eines Summers wechseln. Sie haben auch die Wahl, einen lichtabhängigen Widerstand mit

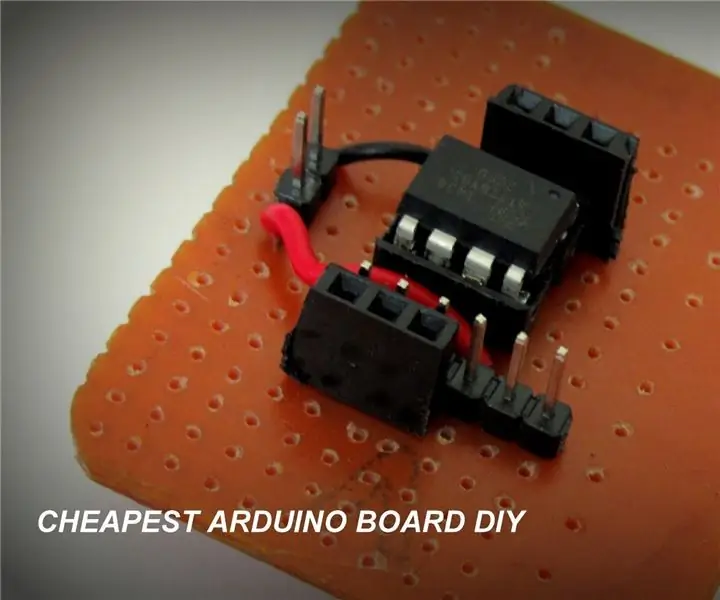

Ein günstiges Attiny Arduino Board herstellen – wikiHow

Wie man ein billiges Attiny Arduino Board herstellt: Nun, die meiste Zeit bekomme ich Probleme, wenn ich Arduino in einigen Projekten benötige, bei denen ich nur wenige I / O-Pins benötige 85/45Arduino-Tiny ist ein Open-Source-Set von ATtiny

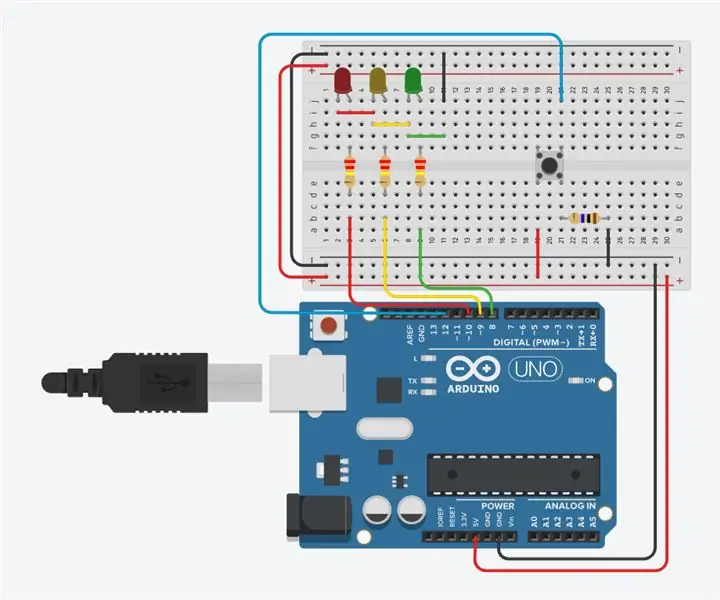

So erstellen Sie eine funktionierende Ampel mit einem Auduino-Board – wikiHow

So erstellen Sie eine funktionierende Ampel mit einem Auduino-Board: Ampeln sind Signalgeräte, die häufig an Straßenkreuzungen, Fußgängerüberwegen und anderen Orten verwendet werden, um den Verkehrsfluss zu steuern. Eine handbetätigte Gasampel war die erste ihrer Art und die Technologie hat die Si

So erstellen Sie Ihr eigenes Arduino-Board (xduino) – wikiHow

So erstellen Sie Ihr eigenes Arduino-Board (xduino): Video ansehen

Jeder Liter zählt! Arduino Wasserdosierer "Shield": 7 Schritte (mit Bildern)

Jeder Liter zählt! Arduino Wasserdosierer "Shield": Hallo! Mit diesem anweisbaren können Sie eine gewünschte Menge Wasser dosieren. Das System kann in ml und L arbeiten. Wir verwenden ein Arduino UNO, einen Durchflussmesser zum Zählen der Wassermenge, ein LCD zur Anzeige des Status, Drucktasten zum Ändern der Einstellungen und ein Relais zum Wechseln